De ce și cum să utilizați FPGA-urile Efinix pentru imagistica AI/ML Partea 2: Captarea și procesarea imaginilor

Contributed By DigiKey's European Editors

2023-05-05

Nota editorului: Noile abordări ale arhitecturilor FPGA aduc un control mai fin și o mai mare flexibilitate pentru a răspunde nevoilor de învățare automată (ML) și inteligență artificială (AI). Partea 1 a acestei serii din două părți prezintă o astfel de arhitectură de la Efinix și arată cum să începeți să o utilizați, folosind o placă de dezvoltare. În partea a 2-a se discută despre interfațarea plăcii de dezvoltare cu dispozitive și componente periferice externe, cum ar fi o cameră foto, și despre cum se poate utiliza FPGA pentru a elimina blocajele în procesarea imaginilor.

FPGA-urile au un rol esențial în multe aplicații, de la controlul și siguranța industrială la aplicațiile robotice, aerospațiale și auto. Datorită naturii flexibile a nucleului logic programabil și capacităților lor largi de interfațare, una dintre utilizările tot mai dese ale FPGA-urilor este procesarea imaginilor, atunci când se poate implementa învățarea automată (ML). Datorită structurii lor logice paralele, FPGA-urile sunt ideale pentru implementarea soluțiilor care au mai multe interfețe de cameră de mare viteză. În plus, FPGA-urile permit și utilizarea unui canal de procesare dedicat în logică, eliminând astfel blocajele de resurse partajate care ar fi asociate cu soluțiile bazate pe CPU sau GPU.

Această a doua prezentare a FPGA-urilor Titanium de la Efinix va examina aplicația de referință pentru procesarea imaginilor, care vine cu placa de dezvoltare Ti180 M484 a FPGA-ului. Scopul este de a înțelege părțile constituente ale proiectului și de a identifica situațiile în care tehnologia FPGA permite eliminarea blocajelor sau oferă alte beneficii dezvoltatorilor.

Proiectul de referință bazat pe Ti180 M484

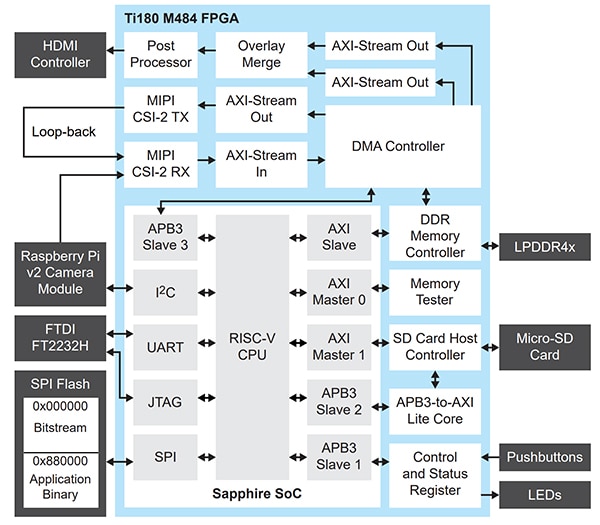

Din punct de vedere conceptual, proiectul de referință (Figura 1) primește imagini de la mai multe camere MIPI (Mobile Industry Processor Interface), realizează tamponarea cadrelor în LPDDR4x și apoi transmite imaginile către un afișaj HDMI (High Definition Multimedia Interface). O placă FPGA Mezzanine Card (FMC) și patru interfețe Samtec QSE de pe placă sunt utilizate pentru a furniza intrările camerei și ieșirea HDMI.

Figura 1: Din punct de vedere conceptual, proiectul de referință Ti180 M484 primește imagini de la mai multe camere MIPI, realizează tamponarea cadrelor în LPDDR4x și apoi transmite imaginile către un afișaj HDMI. >(Sursa imaginii: Efinix)

Figura 1: Din punct de vedere conceptual, proiectul de referință Ti180 M484 primește imagini de la mai multe camere MIPI, realizează tamponarea cadrelor în LPDDR4x și apoi transmite imaginile către un afișaj HDMI. >(Sursa imaginii: Efinix)

Placa de expansiune FMC la QSE este utilizată împreună cu placa secundară HDMI pentru a furniza calea video de ieșire, în timp ce trei conectori QSE sunt utilizați pentru a realiza interfața cu camerele MIPI DFRobot SEN0494. Dacă nu sunt disponibile mai multe camere MIPI, se poate utiliza o singură cameră prin revenirea în buclă la canalul camerei pentru a simula camere suplimentare.

La un nivel înalt, această aplicație poate părea simplă. Cu toate acestea, recepționarea mai multor fluxuri MIPI de înaltă definiție (HD) la o rată mare a cadrelor este o provocare. În acest caz, tehnologia FPGA este benefică, deoarece permite proiectanților să utilizeze mai multe fluxuri MIPI în paralel.

Arhitectura proiectului de referință utilizează structuri de procesare atât paralele, cât și secvențiale cu FPGA. Structurile paralele sunt utilizate pentru a implementa canalul de procesare a imaginilor, în timp ce un procesor RISC-V asigură procesarea secvențială utilizată pentru tabelele de căutare (LUT) ale FPGA.

În cadrul multor sisteme de procesare a imaginilor bazate pe FPGA, canalul de procesare a imaginilor poate fi împărțit în două elemente, și anume în fluxurile de intrare și cele de ieșire. Fluxul de intrare este conectat la interfața cameră/senzor, iar funcțiile de procesare sunt aplicate la ieșirea senzorului. Aceste funcții pot include conversia Bayer, balansul automat al albului și alte îmbunătățiri. În fluxul de ieșire, imaginea este pregătită pentru afișare. Aceasta include schimbarea spațiilor de culoare (de exemplu, RGB în YUV) și postprocesarea pentru formatul de ieșire dorit, cum ar fi HDMI.

Adesea, lanțul de procesare a imaginii de intrare funcționează la frecvența de ceas a pixelilor senzorului. Aceasta are o sincronizare diferită față de lanțul de ieșire, care este procesat la frecvența afișajului de ieșire.

Se utilizează o memorie-tampon de cadre pentru a conecta intrarea la canalul de procesare a ieșirii, care este adesea stocată într-o memorie externă de înaltă performanță, cum ar fi LPDDR4x. Această memorie-tampon de cadre se decuplează între canalele de intrare și ieșire, permițând accesul la memoria-tampon de cadre prin accesul direct al memoriei la frecvența de ceas corespunzătoare.

Proiectul de referință Ti180 utilizează o abordare similară cu conceptele prezentate mai sus. Canalul de procesare a imaginii de intrare implementează un nucleu de proprietate intelectuală (IP) al receptorului MIPI Camera Serial Interface 2 (CSI-2), care este construit pe baza intrărilor/ieșirilor (I/O) compatibile cu stratul fizic MIPI (MIPI D-PHY) ale FPGA Titanium. MIPI este o interfață dificilă, deoarece utilizează atât semnalizarea cu un singur capăt, cât și cea diferențială pe aceeași pereche diferențială, pe lângă comunicațiile de mică și de mare viteză. Integrarea MIPI D-PHY în cadrul FPGA I/O reduce complexitatea proiectării plăcii de circuite, reducând în același timp lista de materiale (BOM).

Odată primit fluxul de imagini de la cameră, proiectul de referință convertește ieșirea MIPI CSI-2 RX într-un flux AXI (Advanced eXtensible Interface). Un flux AXI este o interfață unidirecțională de mare viteză care furnizează un flux de date de la un dispozitiv master la un dispozitiv slave. Se furnizează semnale pentru dialogurile de confirmare pentru transferul între un dispozitiv master și unul slave (tvalid și tready) împreună cu semnale în bandă laterală. Aceste semnale în bandă laterală pot fi utilizate pentru a transmite informații de sincronizare a imaginii, cum ar fi începutul cadrului și sfârșitul liniei.

Fluxul AXI este ideal pentru aplicațiile de procesare a imaginilor și permite companiei Efinix să furnizeze o gamă de proprietate intelectuală pentru procesarea imaginilor, care poate fi apoi integrată cu ușurință în lanțul de procesare, în funcție de cerințele aplicației.

După ce sunt primite, datele de imagine MIPI CSI-2 și semnalele de sincronizare sunt convertite într-un flux AXI și sunt introduse într-un modul de acces direct la memorie (DMA), care inscripționează cadrul imaginii pe LPDDR4x și acționează ca o memorie-tampon de cadre.

Acest modul DMA funcționează sub controlul nucleului RISC-V din FPGA în cadrul unui sistem pe cip (SoC) Sapphire. Acest SoC asigură controlul, cum ar fi oprirea și pornirea inscripționărilor DMA, în plus față de furnizarea canalului de inscripționare DMA cu informațiile necesare pentru a scrie corect datele de imagine pe LPDDR4x. Aceasta include informații privind locația memoriei și lățimea și înălțimea imaginii definite în octeți.

Canalul de ieșire din proiectul de referință citește informațiile de imagine din memoria-tampon de cadre LPDDR4x aflată sub controlul SoC RISC-V. Datele sunt transmise din IP DMA sub forma unui flux AXI, care este apoi convertit din formatul RAW furnizat de senzor în format RGB (Figura 2) și pregătit pentru a fi transmis prin intermediul emițătorului HDMI integrat ADV7511 de la Analog Devices.

Figura 2: Exemple de imagini de ieșire din proiectul de referință. (Sursa imaginii: Adam Taylor)

Figura 2: Exemple de imagini de ieșire din proiectul de referință. (Sursa imaginii: Adam Taylor)

Utilizarea DMA permite, de asemenea, ca Sapphire SoC RISC-V să acceseze imaginile stocate în memoria-tampon de cadre, precum și statisticile abstracte și informațiile despre imagine. În plus, SoC-ul Sapphire este capabil să scrie suprapuneri în LPDDR4x, astfel ca acestea să poată fi îmbinate cu fluxul video de ieșire.

Senzorii de imagine CMOS (CIS) moderni au mai multe moduri de funcționare și pot fi configurați pentru a oferi procesare pe cip, precum și mai multe formate de ieșire și scheme de ceas diferite. Această configurație este furnizată în mod normal prin intermediul unei interfețe I²C. În proiectul de referință Efinix, această comunicare I²C cu camerele MIPI este asigurată de procesorul Sapphire SoC RISC-V.

Integrarea procesorului RISC-V în cadrul FPGA Titanium reduce dimensiunea totală a soluției finale, deoarece elimină necesitatea de a implementa atât dispozitive complexe de stare FPGA, care cresc riscul de proiectare, cât și procesoare externe care măresc lista de materiale.

De asemenea, includerea procesorului asigură compatibilitatea cu IP suplimentar pentru comunicarea cu cardul MicroSD. Acest lucru permite aplicații din lumea reală în care este posibil să fie necesară stocarea imaginilor pentru analize ulterioare.

În general, arhitectura proiectului de referință Ti180 este optimizată pentru a permite o soluție compactă, necostisitoare, dar de înaltă performanță, care permite dezvoltatorilor să reducă costul BOM prin integrarea sistemului.

Unul dintre avantajele cheie ale proiectelor de referință este acela că pot fi utilizate pentru a lansa dezvoltarea de aplicații pe hardware personalizat, permițând dezvoltatorilor să preia elemente critice ale proiectului și să se bazeze pe ele pentru adaptările necesare. Aceasta include capacitatea de a utiliza fluxul TinyML de la Efinix pentru implementarea aplicațiilor TinyML bazate pe vedere care rulează pe FPGA. Acest lucru poate valorifica atât natura paralelă a logicii FPGA, cât și capacitatea de a adăuga cu ușurință instrucțiuni personalizate în procesoarele RISC-V, permițând crearea de acceleratoare în cadrul logicii FPGA.

Implementare

După cum s-a discutat în Partea 1, arhitectura Efinix este unică prin faptul că utilizează celule XLR (eXchangeable Logic and Routing) pentru a asigura atât funcționalitatea de rutare, cât și cea logică. Un sistem video, cum ar fi proiectul de referință, este un sistem mixt care este atât logic, cât și de rutare: este nevoie de o logică extinsă pentru implementarea caracteristicilor de procesare a imaginii și de o rutare extinsă pentru a conecta celulele IP la frecvențele necesare.

Proiectul de referință utilizează aproximativ 42% din celulele XLR din cadrul dispozitivului, lăsând spațiu suficient pentru suplimentări, inclusiv aplicații personalizate, cum ar fi ML periferic.

Utilizarea blocurilor RAM și a blocurilor de procesare a semnalelor digitale (DSP) este, de asemenea, foarte eficientă, fiind folosit doar 4 din cele 640 de blocuri DSP și 40% din blocurile de memorie (Figura 3).

|

Figura 3: Alocarea resurselor pe arhitectura Efinix arată că doar 42% din celulele XLR sunt utilizate, lăsând loc suficient pentru procese suplimentare. (Sursa imaginii: Adam Taylor)

La intrarea/ieșirea dispozitivului, interfața DDR pentru LPDDR4x este utilizată pentru a furniza memoria de aplicație pentru SoC Sapphire și pentru memoriile-tampon de cadre de imagine. Toate resursele MIPI dedicate dispozitivului sunt utilizate împreună cu 50% din buclele de blocare a fazei (Figura 4).

|

Figura 4: Instantaneu al interfeței și al resurselor I/O utilizate. (Sursa imaginii: Adam Taylor)

Intrarea/ieșirea de uz general (GPIO) este utilizată pentru a asigura comunicațiile I²C împreună cu mai multe interfețe conectate la SoC Sapphire, inclusiv NOR FLASH, USB UART și cardul SD. HSIO este utilizat pentru a furniza ieșirea video de mare viteză către transmițătorul HDMI ADC7511.

Unul dintre elementele cruciale atunci când se proiectează cu FPGA-uri nu este doar implementarea și adaptarea proiectului în FPGA, ci și capacitatea de a plasa proiectul logic în FPGA și de a obține performanța de sincronizare necesară atunci când este rutat.

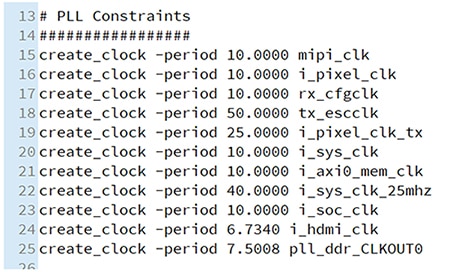

Au trecut demult zilele proiectelor FPGA cu domenii cu un singur ceas. Există mai multe ceasuri diferite, toate rulând la frecvențe ridicate în proiectul de referință Ti180. Tabelul final de sincronizare prezintă frecvențele maxime obținute pentru ceasurile din cadrul sistemului. În acest caz, performanța de sincronizare solicitată poate fi observată și în constrângeri (Figura 5), care au o frecvență maximă de 148,5 megahertzi (MHz) pentru ceasul de ieșire HDMI.

Figura 5: Constrângerile de ceas pentru proiectul de referință. (Sursa imaginii: Adam Taylor)

Figura 5: Constrângerile de ceas pentru proiectul de referință. (Sursa imaginii: Adam Taylor)

Implementarea temporizării în funcție de constrângeri arată potențialul structurii Titanium FPGA XLR, deoarece reduce posibilele întârzieri de rutare, crescând astfel performanța proiectului (Figura 6).

|

Figura 6: Implementarea temporizării în funcție de constrângeri arată potențialul structurii Titanium FPGA XLR de a reduce posibilele întârzieri de rutare, crescând astfel performanța proiectului. (Sursa imaginii: Adam Taylor)

Concluzie

Proiectul de referință Ti180 M484 prezintă în mod clar capacitățile FPGA-urilor Efinix și ale Ti180 în special. Proiectul utilizează câteva dintre structurile unice de I/O pentru a implementa o cale complexă de procesare a imaginilor care acceptă mai multe fluxuri MIPI de intrare. Acest sistem de procesare a imaginilor funcționează sub controlul unui SoC Sapphire soft-core, care implementează elementele de procesare secvențială necesare aplicației.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.