De ce și cum să folosiți FPGA-urile Efinix pentru imagistica AI/ML – Partea 1: Noțiuni introductive

Contributed By DigiKey's European Editors

2023-04-20

Nota editorului: Noile abordări ale arhitecturilor FPGA aduc un control mai fin și o mai mare flexibilitate pentru a răspunde nevoilor de învățare automată (ML) și inteligență artificială (AI). Partea 1 a acestei serii din două părți prezintă o astfel de arhitectură de la Efinix și arată cum să începeți să o utilizați, folosind o placă de dezvoltare. Partea a 2-a tratează interfața dintre placa de dezvoltare și dispozitivele și perifericele externe, cum ar fi o cameră foto.

FPGA-urile au un rol esențial în multe aplicații, de la controlul și siguranța industrială la aplicațiile robotice, aerospațiale și auto. Datorită naturii flexibile a nucleului logic programabil și capacităților lor largi de interfațare, una dintre utilizările tot mai dese ale FPGA-urilor este procesarea imaginilor atunci când trebuie implementată inferența ML. FPGA-urile sunt ideale pentru implementarea soluțiilor care au mai multe interfețe de cameră de mare viteză. În plus, FPGA-urile permit și implementarea de canale de procesare dedicate în logică, eliminând astfel blocajele care ar fi asociate cu soluțiile bazate pe CPU sau GPU.

Cu toate acestea, pentru mulți dezvoltatori, aplicațiile lor necesită mai multe funcționalități ML/AI și un control mai fin al rutării și logicii, dincolo de ceea ce pot oferi arhitecturile FPGA clasice cu blocuri logice combinaționale (CLB). Abordările mai noi ale arhitecturilor FPGA tratează aceste probleme. De exemplu, arhitectura Quantum de la Efinix utilizează un bloc XLR (eXchangeable Logic and Routing – Logică și rutare schimbabilă).

Acest articol discută caracteristicile și atributele cheie ale arhitecturii FPGA Efinix, subliniind capacitățile sale AI/ML și prezentând implementări din lumea reală. Apoi, discută despre o placă de dezvoltare și despre instrumentele asociate pe care dezvoltatorii le pot utiliza pentru a începe rapid proiectarea următoarei lor imagini AI/ML.

Dispozitive FPGA Efinix

Efinix oferă în prezent două game de dispozitive. Inițial, a introdus familia Trion, care oferă densități logice de la 4000 (4K) la 120.000 de elemente logice (LE) și este fabricată folosind un proces SMIC 40LL. Cea mai nouă linie de dispozitive, familia Titanium, oferă densități logice de la 35.000 la 1 milion (1M) de elemente logice și este fabricată pe nodul foarte popular TSMC de 16 nanometri (nm).

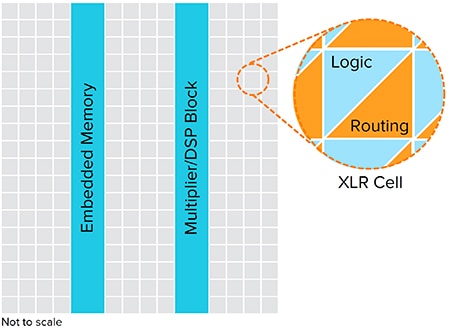

Ambele oferte se bazează pe arhitectura Quantum, care este unică în lumea FPGA. Arhitectura standard FPGA se bazează pe CLB-uri care, la cel mai simplu nivel, conțin un tabel de căutare (LUT) și flip-flop-uri. CLB-urile implementează ecuații logice care sunt apoi interconectate prin rutare. Arhitectura Quantum de la Efinix se îndepărtează de blocurile logice și de rutare distincte cu ajutorul blocului XLR.

Ceea ce face ca un bloc XLR să fie unic este faptul că poate fi configurat pentru a funcționa ca o celulă logică cu un LUT, un registru și un sumator sau o matrice de rutare. Această abordare oferă o arhitectură mai fină, care oferă flexibilitate în ceea ce privește rutarea, permițând ca implementările care au un grad ridicat de logică sau de rutare să atingă performanța dorită.

Figura 1: Ceea ce face ca un bloc XLR să fie unic este faptul că poate fi configurat pentru a funcționa fie ca o celulă logică cu un LUT, un registru și un sumator, fie ca o matrice de rutare. (Sursa imaginii: Efinix)

Figura 1: Ceea ce face ca un bloc XLR să fie unic este faptul că poate fi configurat pentru a funcționa fie ca o celulă logică cu un LUT, un registru și un sumator, fie ca o matrice de rutare. (Sursa imaginii: Efinix)

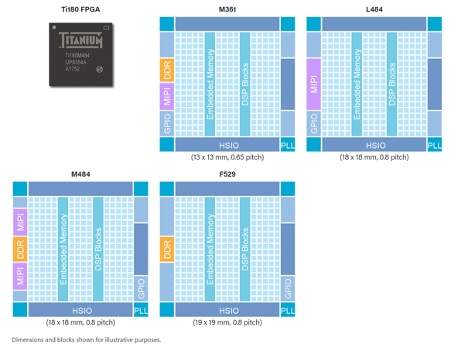

Fiind cea mai nouă familie, dispozitivele Titanium oferă cele mai avansate caracteristici pentru dezvoltatori (Figura 2). Împreună cu nucleul XLR, acestea oferă legături seriale multi-gigabit care funcționează fie la 16 gigabiți pe secundă (Gbps), fie la 25,8 Gbps, în funcție de dispozitivul selectat. Aceste legături multi-gigabit sunt esențiale pentru a permite transferul de date de mare viteză în interiorul și în afara cipului.

Figura 2: FPGA Titanium Ti180 este disponibil într-o varietate de opțiuni, în funcție de lățimea magistralei, de cerințele de I/O și de memorie. (Sursa imaginii: Efinix)

Figura 2: FPGA Titanium Ti180 este disponibil într-o varietate de opțiuni, în funcție de lățimea magistralei, de cerințele de I/O și de memorie. (Sursa imaginii: Efinix)

De asemenea, dispozitivele Titanium oferă o gamă largă de capacități de interfațare de intrare/ieșire (I/O) care pot fi grupate ca I/O de uz general (GPIO) și care pot accepta standarde I/O cu un singur capăt, cum ar fi CMOS de joasă tensiune (LVCMOS) la 3,3 volți, 2,5 volți și 1,8 volți.

Pentru interfațarea de mare viteză și diferențială, dispozitivele Titanium oferă I/O de mare viteză (HSIO) care acceptă standarde I/O cu un singur capăt, cum ar fi LVCMOS la 1,2 volți, 1,5 volți și SSTL și HSTL. Standardele de I/O diferențiale acceptate de HSIO includ semnalizarea diferențială de joasă tensiune (LVDS), SSTL diferențială și HSTL.

De asemenea, FPGA-urile moderne necesită o memorie cu lățime de bandă mare, strâns cuplată, care este utilizată pentru a stoca cadrele de imagine pentru aplicațiile de procesare a imaginilor, datele de eșantionare pentru procesarea semnalelor și, bineînțeles, pentru a rula sistemele de operare și software-ul pentru procesoarele implementate în FPGA. Gama de dispozitive Titanium oferă capacitatea de interfațare cu DDR4 (rată dinamică de transfer al datelor de a patra generație) și DDR4(x) cu consum redus de energie (LPDDR4(x)). În funcție de dispozitivul Titanium selectat, suportul pentru lățimea magistralei este x32 (J) sau x16 (M), în timp ce unele dispozitive nu au suport LPDDR4 (L).

FPGA-urile Titanium sunt bazate pe SRAM și necesită o memorie de configurare, configurarea dispozitivului fiind realizată fie prin intermediul interfeței seriale periferice SPI (Serial Peripheral Interconnect) master/slave, fie prin JTAG. Pentru a garanta că această metodă de configurare este sigură, Titanium FPGA utilizează criptarea AES GCM a fluxului de biți, împreună cu AES GCM și RSA-4096 pentru a asigura autentificarea fluxului de biți. O astfel de securitate puternică este necesară deoarece FPGA-urile sunt implementate la periferie, unde actorii rău-intenționați ar putea accesa și manipula comportamentul lor.

Introducerea plăcilor de dezvoltare

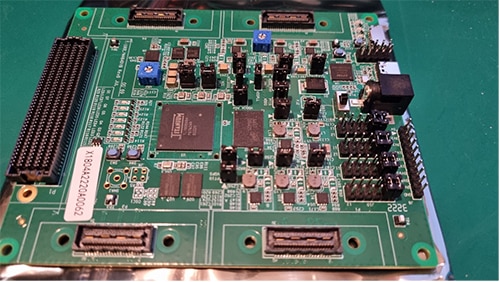

Plăcile de dezvoltare constituie un element esențial al procesului de evaluare a FPGA, deoarece pot fi utilizate pentru a explora capacitățile unui dispozitiv și pentru a crea prototipuri de aplicații, contribuind astfel la reducerea riscului general. Prima placă de dezvoltare disponibilă pentru a evalua FPGA-urile Titanium și pentru a începe prototiparea aplicațiilor este Ti180 M484 (Figura 3). Placa dispune de un conector FPGA Mezzanine Card (FMC) și de patru conectori Samtec QSE.

Figura 3: Împreună cu un FPGA Titanium, kitul de dezvoltare Ti180 M484 dispune de un conector FMC și patru conectori Samtec QSE. (Sursa imaginii: Adam Taylor)

Figura 3: Împreună cu un FPGA Titanium, kitul de dezvoltare Ti180 M484 dispune de un conector FMC și patru conectori Samtec QSE. (Sursa imaginii: Adam Taylor)

FPGA Ti180 montat pe această placă de dezvoltare oferă 172.000 de celule XLR, 32 de ceasuri globale, 640 de elemente de procesare a semnalelor digitale (DSP) și 13 megabiți (Mbit) de memorie RAM încorporată. Elementele DSP oferă capacitatea de a implementa înmulțiri 18 x 19 în virgulă fixă și înmulțiri pe 48 de biți. De asemenea, acest DSP poate fi optimizat pentru operații SIMD (instrucțiune unică, date multiple) care rulează într-o configurație dublă sau cvadruplă. Elementele DSP pot fi, de asemenea, configurate pentru a efectua operații în virgulă mobilă.

La fel ca majoritatea plăcilor de dezvoltare, placa de dezvoltare Ti180 oferă leduri și butoane simple. Cu toate acestea, adevărata sa putere constă în capacitățile sale de interfațare. Placa de dezvoltare Ti180 oferă un conector FMC cu număr redus de pini care permite conectarea unei game largi de periferice. Deoarece este un standard utilizat pe scară largă, există multe carduri FMC care permit interfațarea convertorului analogic-digital (ADC) de mare viteză, a convertorului digital-analogic (DAC), a rețelelor și a soluțiilor de memorie/stocare.

În plus față de conexiunea FMC, placa oferă patru conectori Samtec QSE care permit dezvoltatorului să adauge plăci de expansiune. Acești conectori QSE sunt utilizați pentru a furniza intrări și ieșiri MIPI, fiecare conector QSE furnizând fie o intrare, fie o ieșire MIPI.

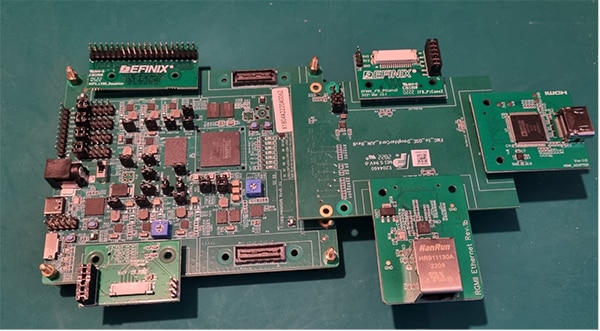

Figura 4: Kitul de dezvoltare Ti180 M484 este prezentat cu gama sa versatilă de opțiuni de expansiune bazate pe conectori QSE și FMC. (Sursa imaginii: Adam Taylor)

Figura 4: Kitul de dezvoltare Ti180 M484 este prezentat cu gama sa versatilă de opțiuni de expansiune bazate pe conectori QSE și FMC. (Sursa imaginii: Adam Taylor)

Placa Ti180 oferă, de asemenea, 256 Mbiți de LPDDR4 pentru a susține memoria de înaltă performanță necesară în aplicațiile de procesare a imaginilor sau a semnalelor. În plus, placa de dezvoltare oferă o gamă de opțiuni de sincronizare la 25, 33,33, 50 și 74,25 megahertzi (MHz), care pot fi utilizate cu bucla blocată în fază (PLL) a dispozitivului pentru a genera diferite frecvențe interne.

Capacitatea de reprogramare și de depanare live pe placă în timpul dezvoltării este esențială și necesită o conexiune JTAG, care este integrată prin intermediul unei interfețe USB-C. De asemenea, este furnizată și o memorie nevolatilă sub forma a două dispozitive flash NOR de 256 Mbiți care pot fi utilizate pentru a demonstra soluția de configurare.

Placa este alimentată de la un adaptor de alimentare universal de 12 volți, inclus în cutie. De asemenea, este inclusă o ieșire FMC la QSE, împreună cu plăci de expansiune bazate pe QSE pentru HDMI, Ethernet, MIPI și LVDS. Pentru a demonstra capacitățile de procesare a imaginilor Ti180, sunt furnizate, de asemenea, o placă secundară RPI dublă și două plăci de cameră IMX477.

Mediul software

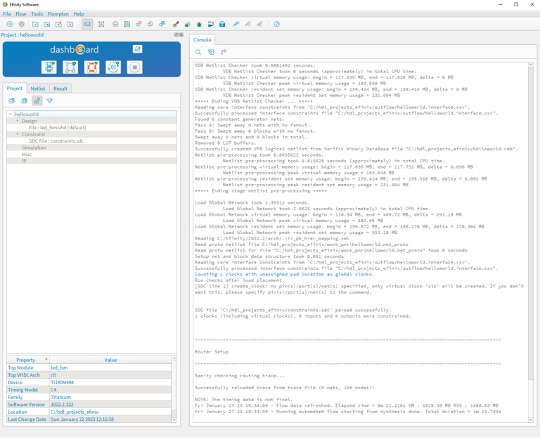

Proiectele de implementare care vizează placa de dezvoltare Ti180 utilizează software-ul Efinix Efinity. Software-ul permite generarea unui flux de biți prin sinteză și plasare și rutare. De asemenea, oferă dezvoltatorilor blocuri de proprietate intelectuală (IP), analiză de sincronizare și depanare pe cip.

Rețineți că este nevoie de o placă de dezvoltare pentru a avea acces la software-ul Efinity. Totuși, spre deosebire de alți furnizori, instrumentul nu are versiuni diferite care necesită licențe suplimentare.

În cadrul Efinity se creează proiecte noi care vizează dispozitivul selectat. Fișierele RTL pot fi apoi adăugate la proiect și se pot crea constrângeri pentru sincronizare și proiectare I/O. În cadrul Efinity, dezvoltatorii au posibilitatea de a implementa designul I/O, utilizând HSIO, GPIO și I/O specializate.

Figura 5: În cadrul Efinity se creează proiecte noi care vizează dispozitivul selectat. (Sursa imaginii: Adam Taylor)

Figura 5: În cadrul Efinity se creează proiecte noi care vizează dispozitivul selectat. (Sursa imaginii: Adam Taylor)

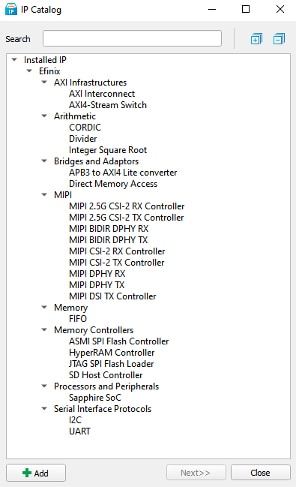

Un element critic al proiectării FPGA este valorificarea IP, în special pentru IP complexe, cum ar fi interconexiunile AXI, controlerele de memorie și procesoarele softcore. Efinity pune la dispoziția dezvoltatorilor o gamă de blocuri IP care pot fi utilizate pentru a accelera procesul de proiectare.

Figura 6: Efinity oferă dezvoltatorilor un catalog IP pe care îl pot utiliza pentru a accelera procesul de proiectare. (Sursa imaginii: Adam Taylor)

Figura 6: Efinity oferă dezvoltatorilor un catalog IP pe care îl pot utiliza pentru a accelera procesul de proiectare. (Sursa imaginii: Adam Taylor)

Deși FPGA-urile sunt excelente pentru implementarea structurilor de procesare paralelă, multe modele FPGA includ procesoare softcore. Acestea oferă capacitatea de a implementa procesarea secvențială, cum ar fi comunicațiile în rețea. Pentru a permite implementarea procesoarelor softcore în dispozitivele Efinix, Efinity oferă instrumentul de configurare a sistemului pe cip (SoC) Sapphire. Sapphire permite dezvoltatorului să definească un sistem multiprocesor care are atât memoria cache, cât și coerența cache pe mai multe procesoare, împreună cu capacitatea de a rula un sistem de operare Linux încorporat. În cadrul Sapphire, dezvoltatorul poate alege între unul și patru procesoare softcore.

Procesorul softcore implementat este procesorul soft CPU VexRiscV, care se bazează pe arhitectura RISC-V cu set de instrucțiuni. Procesorul VexRiscV este o implementare pe 32 de biți care are extensii pentru crearea canalelor și oferă un set de caracteristici configurabile, ceea ce îl face ideal pentru implementarea în dispozitivele Efinix. Configurațiile opționale includ un multiplicator, instrucțiuni atomice, extensii în virgulă mobilă și instrucțiuni comprimate. În funcție de configurația sistemului SoC, performanța va varia între 0,86 și 1,05 DMIPS/MHz.

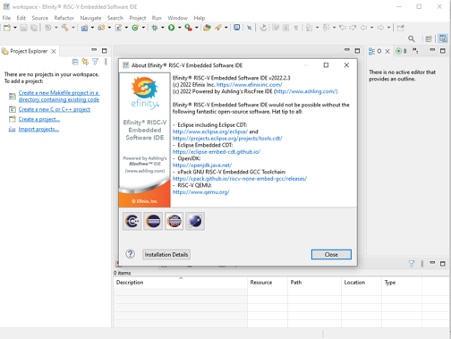

Odată ce mediul hardware a fost proiectat și implementat în dispozitivul Efinix, software-ul de aplicație poate fi dezvoltat cu ajutorul IDE-ului Ashling RiscFree. Ashling RiscFree este un IDE bazat pe Eclipse care permite crearea și compilarea de software de aplicație, împreună cu depanarea pe țintă pentru a regla fin aplicația înainte de implementare.

Figura 7: Ashling RiscFree este un IDE bazat pe Eclipse care permite crearea și compilarea de software de aplicație, precum și depanarea pe țintă. (Sursa imaginii: Adam Taylor)

Figura 7: Ashling RiscFree este un IDE bazat pe Eclipse care permite crearea și compilarea de software de aplicație, precum și depanarea pe țintă. (Sursa imaginii: Adam Taylor)

În cazul în care se dezvoltă o soluție Linux încorporată, sunt furnizate toate artefactele de inițializare necesare, inclusiv First Stage Boot Loader, OpenSBI, U-Boot și Linux utilizând Buildroot. Alternativ, dezvoltatorul poate utiliza FreeRTOS dacă este nevoie de o soluție în timp real.

Implementarea AI

Implementarea inteligenței artificiale a Efinix se bazează pe operațiunea RISC-V softcore. Aceasta valorifică capacitatea de instrucțiuni personalizate a procesorului RISC-V pentru a permite accelerarea soluțiilor TensorFlow Lite. De asemenea, utilizarea procesorului RISC-V permite utilizatorilor să creeze instrucțiuni personalizate care pot fi utilizate ca parte a pre-procesării sau post-procesării în urma inferenței AI, creând o soluție mai receptivă și mai deterministă.

Pentru a începe o implementare AI, primul pas este să explorați Efinix Model Zoo, care este o bibliotecă de modele AI/ML optimizate pentru tehnologia finală. Dezvoltatorii care lucrează cu dispozitivele Efinix pot accesa Model Zoo și pot instrui rețeaua folosind Jupyter Notebooks sau Google Colab. După ce rețeaua a fost instruită, aceasta poate fi convertită dintr-un model în virgulă mobilă într-unul cuantificat cu ajutorul convertorului TensorFlow Lite.

Odată ajunsă în formatul TensorFlow Lite, se poate utiliza acceleratorul tinyML de la Efinix pentru a crea o soluție implementabilă pe soluția RISC-V. Generatorul tinyML permite dezvoltatorului să personalizeze implementarea acceleratorului și să genereze fișierele de proiect. Atunci când este implementată în acest mod, accelerația poate varia între 4 și 200x, în funcție de arhitectura și personalizarea selectate.

Concluzie

Dispozitivele Efinix oferă dezvoltatorilor flexibilitate datorită arhitecturii lor XLR unice. Lanțul de instrumente oferă capacitatea de a implementa nu numai proiectarea RTL, ci și soluții SoC complexe care utilizează procesoare RISC-V softcore. Pe lângă SoC-ul softcore se află o soluție AI/ML care permite implementarea inferenței ML.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.