Utilizați calea rapidă FPGA pentru a construi aplicații IA aproape de sursă, de înaltă performanță și cu consum redus de energie

Contributed By DigiKey's North American Editors

2021-01-12

Proiectanții care doresc să implementeze algoritmi de inteligență artificială (IA) pe procesoarele de inferență aproape de sursă sunt mereu sub presiunea de a reduce consumul de energie și timpul de dezvoltare, odată cu creșterea cerințelor de procesare. Rețelele de porți programabile în câmp (FPGA-uri) oferă o combinație deosebit de eficientă între viteză și eficiență energetică pentru implementarea motoarelor de inferență ale rețelelor neuronale (NN) necesare pentru inteligența artificială aproape de sursă. Cu toate acestea, pentru dezvoltatorii care nu sunt familiarizați cu FPGA-urile, metodele convenționale de dezvoltare FPGA pot părea complexe, ceea ce, de multe ori, îi determină să apeleze la soluții mai puțin optime.

Acest articol prezintă o abordare mai simplă de la Microchip Technology, care permite dezvoltatorilor să ocolească dezvoltarea tradițională a FPGA-urilor pentru a crea NN-uri antrenate prin intermediul FPGA-urilor și al unui kit de dezvoltare software (SDK) sau să utilizeze un kit video bazat pe FPGA pentru a trece imediat la dezvoltarea de aplicații de vizualizare inteligentă încorporată.

De ce să folosiți inteligența artificială aproape de sursă?

Noțiunea de Edge Computing aduce o serie de beneficii pentru aplicațiile Internet of Things (IoT) în diferite segmente, precum automatizarea industrială, sistemele de securitate, casele inteligente și multe altele. Într-o aplicație Industrial IoT (IIoT) care vizează nivelul de producție, Edge Computing poate îmbunătăți dramatic timpul de răspuns în buclele de control al proceselor prin eliminarea întârzierilor de retur către aplicațiile pe bază de cloud. În mod similar, un sistem de securitate bazat pe Edge Computing sau o încuietoare inteligentă pentru ușa casei poate continua să funcționeze chiar și atunci când conexiunea la cloud este pierdută în mod accidental sau intenționat. În multe cazuri, utilizarea soluțiilor Edge Computing în oricare dintre aceste aplicații poate contribui la reducerea costurilor totale de operare prin reducerea dependenței produsului de resursele cloud. În loc să se confrunte cu o nevoie neașteptată de resurse cloud suplimentare costisitoare, pe măsură ce cererea pentru produsele lor crește, dezvoltatorii se pot baza pe capacitățile de procesare locale încorporate în produsele lor, pentru a contribui la menținerea unor cheltuieli de operare mai stabile.

Acceptarea rapidă și cererea crescută de modele de inferență pentru învățare automatizată (ML) amplifică în mod dramatic importanța soluțiilor Edge Computing. Pentru dezvoltatori, procesarea locală a modelelor de inferență ajută la reducerea latenței de răspuns și a costurilor pentru resursele cloud necesare pentru inferența bazată pe cloud. Pentru utilizatori, utilizarea modelelor de inferență locală sporește încrederea în faptul că produsele lor vor continua să funcționeze și în cazul pierderii ocazionale a conectivității la internet sau al schimbărilor în ofertele bazate pe cloud ale furnizorului de produse. În plus, preocupările legate de securitate și confidențialitate pot determina și mai mult nevoia de procesare locală și de inferență, pentru a limita cantitatea de informații sensibile transferate în cloud prin internetul public.

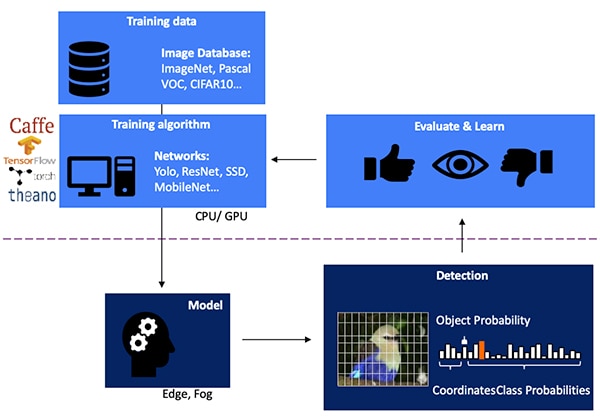

Dezvoltarea unui model de inferență NN pentru detectarea obiectelor pe bază de vizualizare este un proces cu mai multe etape, care începe cu antrenarea modelelor, de obicei realizată pe un cadru ML, cum ar fi TensorFlow, folosind imagini etichetate disponibile public sau imagini etichetate personalizate. Din cauza cerințelor de procesare, antrenarea modelelor se realizează, de obicei, cu unități de procesare grafică (GPU) în cloud sau pe o altă platformă de calcul de înaltă performanță. După finalizarea antrenării, modelul este convertit într-un model de inferență capabil să ruleze pe resurse de calcul de tip Edge sau Fog Computing și să furnizeze rezultatele inferenței sub forma unui set de probabilități pe clase de obiecte (Figura 1).

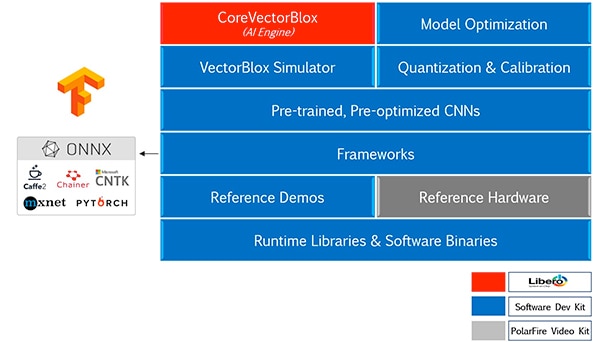

Figura 1: implementarea unui model de inferență pentru inteligența artificială aproape de sursă se află la capătul unui proces cu mai multe etape care necesită antrenarea și optimizarea NN-urilor pe cadre care folosesc date de instruire disponibile sau personalizate. (Sursă imagine: Microchip Technology)

Figura 1: implementarea unui model de inferență pentru inteligența artificială aproape de sursă se află la capătul unui proces cu mai multe etape care necesită antrenarea și optimizarea NN-urilor pe cadre care folosesc date de instruire disponibile sau personalizate. (Sursă imagine: Microchip Technology)

De ce modelele de inferență sunt dificile din punct de vedere computațional

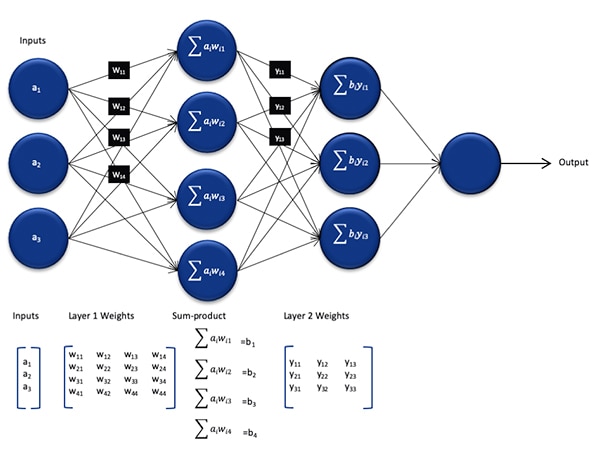

Deși redus ca dimensiune și complexitate în comparație cu modelul utilizat în timpul procesului de antrenare, un model de inferență NN reprezintă încă o provocare computațională pentru procesoarele de uz general, din cauza numărului mare de calcule pe care le necesită. În forma sa generică, un model NN profund cuprinde mai multe niveluri de seturi de neuroni. În cadrul fiecărui nivel dintr-o rețea complet conectată, fiecare neuron nij trebuie să calculeze suma produselor de la fiecare intrare, cu o pondere asociată wij (Figura 2).

Figura 2: numărul de calcule necesare pentru inferența cu un NN poate impune o sarcină de calcul semnificativă. (Sursă imagine: Microchip Technology)

Figura 2: numărul de calcule necesare pentru inferența cu un NN poate impune o sarcină de calcul semnificativă. (Sursă imagine: Microchip Technology)

În Figura 2 nu este prezentată cerința suplimentară de calcul impusă de funcția de activare care modifică ieșirea fiecărui neuron prin maparea valorilor negative la zero, prin maparea valorilor mai mari de 1 la 1 și prin funcții similare. Ieșirea funcției de activare pentru fiecare neuron nij servește ca intrare pentru următorul nivel i+1, continuând în același mod pentru fiecare nivel. În cele din urmă, nivelul de ieșire al modelului NN produce un vector de ieșire ce reprezintă probabilitatea ca vectorul (sau matricea) de intrare original să corespundă uneia dintre clasele (sau etichetele) utilizate în timpul procesului de învățare supravegheată.

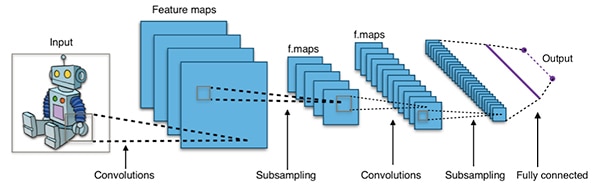

Modelele NN eficiente sunt construite cu arhitecturi care sunt mult mai mari și mai complexe decât arhitectura NN generică reprezentativă prezentată mai sus. De exemplu, o rețea convoluțională NN (CNN) tipică utilizată pentru detectarea obiectelor din imagini aplică aceste principii în mod fragmentat, scanând lățimea, înălțimea și profunzimea culorilor unei imagini de intrare, pentru a produce o serie de hărți de caracteristici care, în final, produc vectorul de predicție de la ieșire (Figura 3).

Figura 3: CNN-urile utilizate pentru detectarea obiectelor din imagini implică un număr mare de neuroni pe mai multe niveluri, ceea ce implică o cerere mai mare asupra platformei de calcul. (Sursă imagine: Aphex34 CC BY-SA 4.0)

Figura 3: CNN-urile utilizate pentru detectarea obiectelor din imagini implică un număr mare de neuroni pe mai multe niveluri, ceea ce implică o cerere mai mare asupra platformei de calcul. (Sursă imagine: Aphex34 CC BY-SA 4.0)

Utilizarea FPGA-urilor pentru accelerarea matematicii NN

Deși continuă să apară o serie de opțiuni pentru executarea modelelor de inferență aproape de sursă, puține alternative oferă o combinație optimă de flexibilitate, performanță și eficiență energetică necesară pentru inferența practică de mare viteză aproape de sursă. Fiind printre alternativele imediat disponibile pentru inteligența artificială aproape de sursă, FPGA-urile sunt deosebit de eficiente, deoarece pot oferi o executare pe bază de hardware de înaltă performanță a operațiilor care necesită putere mare de calcul, consumând în același timp relativ puțină energie.

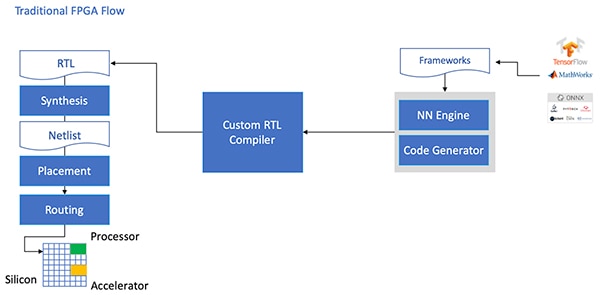

În ciuda avantajelor lor, FPGA-urile sunt uneori ocolite din cauza unui flux de dezvoltare tradițional care poate fi descurajant pentru dezvoltatorii care nu au o experiență vastă în domeniul FPGA. Pentru a crea o implementare FPGA eficientă a unui model NN generat de un cadru NN, dezvoltatorul trebuie să înțeleagă nuanțele de conversie a modelului în limbaj de transfer de registre (RTL), să sintetizeze proiectarea, să lucreze până la etapa finală și să direcționeze etapa de proiectare fizică pentru a produce o implementare optimizată (Figura 4).

Figura 4: pentru a implementa un model NN pe un FPGA, dezvoltatorii au trebuit până acum să înțeleagă modul de convertire a modelelor în RTL și cum să lucreze prin fluxul FPGA tradițional. (Sursă imagine: Microchip Technology)

Figura 4: pentru a implementa un model NN pe un FPGA, dezvoltatorii au trebuit până acum să înțeleagă modul de convertire a modelelor în RTL și cum să lucreze prin fluxul FPGA tradițional. (Sursă imagine: Microchip Technology)

Cu FPGA-urile sale PolarFire, software-ul specializat și proprietatea intelectuală (IP) asociată, Microchip Technology oferă o soluție care face ca inferența de înaltă performanță și cu consum redus de energie aproape de sursă să fie disponibilă pentru dezvoltatorii fără experiență în FPGA.

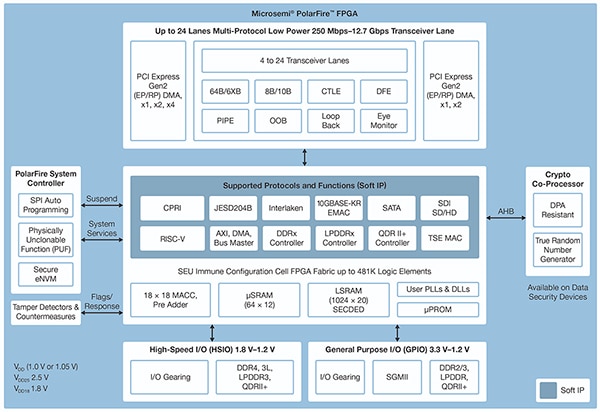

Fabricate cu o tehnologie avansată de procesare non-volatilă, FPGA-urile PolarFire sunt proiectate pentru a maximiza flexibilitatea și performanța, minimizând în același timp consumul de energie. Împreună cu o gamă extinsă de interfețe de mare viteză pentru comunicații și intrări/ieșiri (I/O), acestea dispun de o structură FPGA profundă capabilă să susțină funcționalități avansate, utilizând nuclee IP soft, inclusiv procesoare RISC-V, controlere de memorie avansate și alte subsisteme de interfață standard (Figura 5).

Figura 5: arhitectura PolarFire de la Microchip Technology oferă o structură profundă concepută pentru susținerea cerințelor de proiectare de înaltă performanță, inclusiv implementarea modelelor de inferență care necesită putere mare de calcul. (Sursă imagine: Microchip Technology)

Figura 5: arhitectura PolarFire de la Microchip Technology oferă o structură profundă concepută pentru susținerea cerințelor de proiectare de înaltă performanță, inclusiv implementarea modelelor de inferență care necesită putere mare de calcul. (Sursă imagine: Microchip Technology)

Structura FPGA PolarFire oferă un set extins de elemente logice și blocuri specializate, acceptate într-o gamă de capacități de către diferiți membri ai familiei FPGA PolarFire, inclusiv seriile MPF100T, MPF200T, MPF300T și MPF500T (Tabelul 1).

|

Tabelul 1: în seria PolarFire este disponibilă o varietate de caracteristici și capacități ale structurii FPGA. (Sursă tabel: DigiKey, pe baza fișei tehnice Microchip Technology PolarFire)

Printre caracteristicile de interes deosebit pentru accelerarea inferenței, arhitectura PolarFire include un bloc matematic dedicat care oferă o funcție de multiplicare-acumulare (MAC) pe 18 biți × 18 biți cu semnătură și cu pre-sumator. Un mod încorporat de produs scalar utilizează un singur bloc matematic pentru a efectua două operații de înmulțire pe 8 biți, oferind un mecanism de creștere a capacității prin valorificarea impactului neglijabil al cuantificării modelului asupra preciziei.

Pe lângă accelerarea operațiilor matematice, arhitectura PolarFire ajută la reducerea aglomerării memoriei care apare la implementarea modelelor de inferență pe arhitecturi de uz general, cum ar fi memoriile de mici dimensiuni distribuite pentru stocarea rezultatelor intermediare create în timpul execuției algoritmului NN. De asemenea, ponderile și valorile de polarizare ale unui model NN pot fi stocate într-o memorie doar cu citire (ROM) de 18 biți cu adâncime de 16 biți construită din elemente logice situate în apropierea blocului matematic.

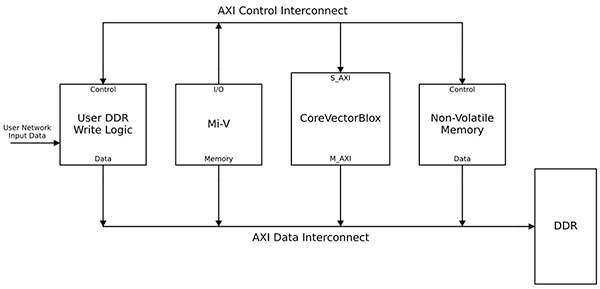

Combinate cu alte caracteristici ale structurii PolarFire FPGA, blocurile matematice oferă baza pentru IP CoreVectorBlox de nivel superior de la Microchip Technology. Acesta servește drept motor NN flexibil, capabil să execute diferite tipuri de NN. Împreună cu un set de registre de control, IP CoreVectorBlox include trei blocuri funcționale majore:

- Microcontroler: un simplu procesor RISC-V soft care citește obiectul binar de mari dimensiuni (BLOB) al firmware-ului Microchip și fișierul NN BLOB specific utilizatorului din memoria externă. Acesta controlează operațiunile generale ale CoreVectorBlox prin executarea instrucțiunilor din BLOB-ul firmware.

- Procesor matrice (MXP): un procesor soft alcătuit din opt unități aritmetice logice pe 32 de biți (ALU), conceput pentru a efectua operații paralele pe vectori de date folosind operații tensoriale pe bază de elemente, inclusiv add, sub, xor, shift, mul, dotprod și altele, folosind precizie mixtă de 8, 16 și 32 de biți, după caz.

- Accelerator CNN: accelerează operațiile MXP utilizând o matrice bidimensională de funcții MAC implementate cu ajutorul blocurilor matematice și care funcționează cu o precizie de 8 biți.

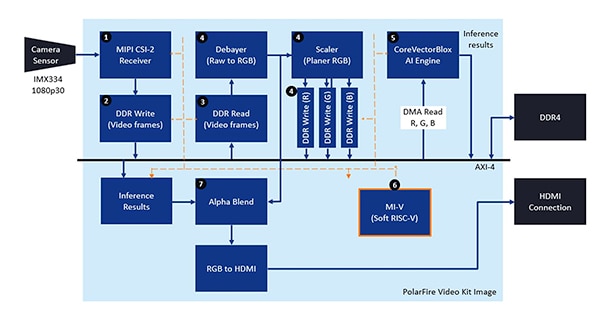

Un sistem complet de procesare NN ar combina un bloc IP CoreVectorBlox, memorie, controler de memorie și un procesor gazdă, cum ar fi nucleul procesorului de software Microsoft RISC-V (Mi-V) (Figura 6).

Figura 6: blocul IP CoreVectorBlox funcționează cu un procesor gazdă, cum ar fi microcontrolerul Mi-V RISC-V de la Microchip, pentru a implementa un model de inferență NN. (Sursă imagine: Microchip Technology)

Figura 6: blocul IP CoreVectorBlox funcționează cu un procesor gazdă, cum ar fi microcontrolerul Mi-V RISC-V de la Microchip, pentru a implementa un model de inferență NN. (Sursă imagine: Microchip Technology)

Într-o implementare a unui sistem video, procesorul gazdă ar încărca firmware-ul și BLOB-urile de rețea din memoria flash a sistemului și le-ar copia în memoria cu acces aleator (RAM) cu viteză dublă de transfer a datelor (DDR) pentru a fi utilizate de blocul CoreVectorBlox. Pe măsură ce sosesc cadrele video, procesorul gazdă le inscripționează în memoria RAM DDR și semnalează blocului CoreVectorBlox să înceapă procesarea imaginii. După ce rulează modelul de inferență definit în BLOB-ul rețelei, blocul CoreVectorBlox scrie rezultatele, inclusiv clasificarea imaginilor, înapoi în memoria RAM DDR, pentru a fi utilizate de aplicația țintă.

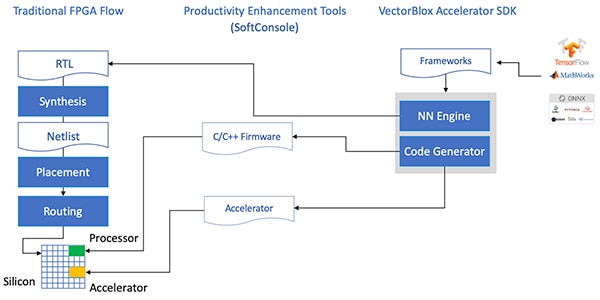

Fluxul de dezvoltare simplifică implementarea NN FPGA

Microchip îi scutește pe dezvoltatori de complexitatea implementării unui model de inferență NN pe FPGA-urile PolarFire. În loc să se ocupe de detaliile fluxului FPGA tradițional, dezvoltatorii de modele NN lucrează ca de obicei cu cadrele NN și încarcă modelul rezultat în kitul de dezvoltare software (SDK) pentru acceleratorul VectorBlox de la Microchip Technology. SDK generează setul necesar de fișiere, inclusiv cele necesare pentru fluxul normal de dezvoltare FPGA și fișierele BLOB pentru firmware și rețea menționate anterior (Figura 7).

Figura 7: SDK pentru acceleratorul VectorBlox gestionează detaliile implementării unui model NN pe un FPGA, generând automat fișierele necesare pentru proiectarea și rularea modelului de inferență bazat pe FPGA. (Sursă imagine: Microchip Technology)

Figura 7: SDK pentru acceleratorul VectorBlox gestionează detaliile implementării unui model NN pe un FPGA, generând automat fișierele necesare pentru proiectarea și rularea modelului de inferență bazat pe FPGA. (Sursă imagine: Microchip Technology)

Deoarece fluxul SDK pentru acceleratorul VectorBlox suprapune proiectarea NN pe motorul NN implementat în FPGA, diferite NN-uri pot rula pe același proiect FPGA fără a fi nevoie să se refacă fluxul de sinteză a proiectului FPGA. Dezvoltatorii creează cod C/C++ pentru sistemul rezultat și pot schimba din mers modelele din cadrul sistemului sau pot rula modelele simultan, utilizând partiționarea în timp.

SDK pentru acceleratorul VectorBlox îmbină suita de proiectare Libero FPGA de la Microchip Technology cu un set complex de funcții pentru dezvoltarea modelului de inferență NN. Împreună cu serviciile de optimizare, cuantificare și calibrare a modelelor, SDK oferă un simulator NN care permite dezvoltatorilor să utilizeze aceleași fișiere BLOB pentru a-și evalua modelul înainte de a-l utiliza în implementarea hardware-ului FPGA (Figura 8).

Figura 8: SDK pentru acceleratorul VectorBlox oferă un set complex de servicii concepute pentru a optimiza implementarea în FPGA a modelelor de inferență generate pe bază de cadre. (Sursă imagine: Microchip Technology)

Figura 8: SDK pentru acceleratorul VectorBlox oferă un set complex de servicii concepute pentru a optimiza implementarea în FPGA a modelelor de inferență generate pe bază de cadre. (Sursă imagine: Microchip Technology)

SDK pentru acceleratorul VectorBlox acceptă modele în formatul Open Neural Network Exchange (ONNX), precum și modele din mai multe cadre, inclusiv TensorFlow, Caffe, Chainer, PyTorch și MXNET. Arhitecturile CNN acceptate includ MNIST, versiunile MobileNet, ResNet-50, Tiny Yolo V2 și Tiny Yolo V3. Microchip lucrează la extinderea compatibilității pentru a include majoritatea rețelelor open-source de modele pre-instruite din sistemul Open Model Zoo pentru kitul de instrumente OpenVINO, inclusiv Yolo V3, Yolo V4, RetinaNet și SSD-MobileNet, printre multe altele.

Kitul video demonstrează inferența FPGA

Pentru a-i ajuta pe dezvoltatori să treacă rapid la dezvoltarea de aplicații inteligente de vizualizare încorporată, Microchip Technology oferă o aplicație de eșantionare complexă, concepută pentru a rula pe kitul pentru video și imagini MPF300-VIDEO-KIT PolarFire FPGA și modelul de referință al companiei.

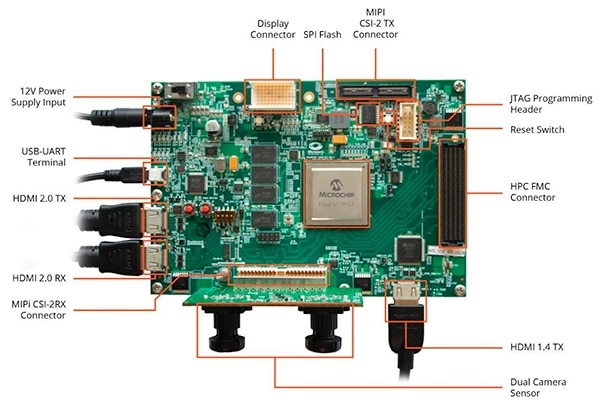

Bazată pe Microchip PolarFire FPGA MPF300T, placa din kit combină un senzor de cameră dual, memorie RAM 4 cu viteză dublă de transfer de date (DDR4), memorie flash, gestionarea energiei și o varietate de interfețe (Figura 9).

Figura 9: kitul pentru video și imagini MPF300-VIDEO-KIT PolarFire FPGA și software-ul asociat oferă dezvoltatorilor un început rapid în lumea inferenței bazate pe FPGA în aplicații inteligente de vizualizare încorporată. (Sursă imagine: Microchip Technology)

Figura 9: kitul pentru video și imagini MPF300-VIDEO-KIT PolarFire FPGA și software-ul asociat oferă dezvoltatorilor un început rapid în lumea inferenței bazate pe FPGA în aplicații inteligente de vizualizare încorporată. (Sursă imagine: Microchip Technology)

Kitul este livrat cu un proiect de design Libero complet, utilizat pentru a genera fișierele BLOB pentru firmware și rețea. După programarea fișierelor BLOB în memoria flash încorporată, dezvoltatorii fac clic pe butonul de execuție din Libero pentru a porni demonstrația, ce procesează imaginile video primite de la senzorul camerei și afișează rezultatele inferenței pe un ecran (Figura 10).

Figura 10: kitul pentru video și imagini FPGA PolarFire de la Microchip Technology demonstrează modul de proiectare și utilizare a implementării FPGA a unui sistem inteligent de vizualizare încorporat, construit în jurul motorului Microchip CoreVectorBlox NN. (Sursă imagine: Microchip Technology)

Figura 10: kitul pentru video și imagini FPGA PolarFire de la Microchip Technology demonstrează modul de proiectare și utilizare a implementării FPGA a unui sistem inteligent de vizualizare încorporat, construit în jurul motorului Microchip CoreVectorBlox NN. (Sursă imagine: Microchip Technology)

Pentru fiecare cadru video de intrare, sistemul bazat pe FPGA execută următorii pași (numerele pașilor se corelează cu cele din Figura 10):

- Încărcați un cadru de la cameră

- Stocați cadrul în RAM

- Citiți cadrul din RAM

- Convertiți imaginea neprelucrată în RGB, în planificatorul RGB și stocați rezultatul în RAM

- Procesorul Mi-V soft RISC-V pornește motorul CoreVectorBlox, care preia imaginea din RAM, efectuează inferența și stochează rezultatele probabilității de clasificare înapoi în RAM

- Mi-V utilizează rezultatele pentru a crea un cadru de suprapunere cu casete de delimitare, rezultate de clasificare și alte metadate și stochează cadrul în memoria RAM

- Cadrul original este combinat cu cadrul de suprapunere și inscripționat pe afișajul HDMI

Demonstrația acceptă accelerarea modelelor Tiny Yolo V3 și MobileNet V2, dar dezvoltatorii pot rula și alte modele acceptate de SDK, utilizând metodele descrise anterior, prin efectuarea unei mici modificări de cod pentru a adăuga numele modelului și metadatele la lista existentă care conține cele două modele implicite.

Concluzie

În mod obișnuit, algoritmii de inteligență artificială, cum ar fi modelele NN, implică sarcini de lucru care necesită putere mare de calcul și resurse de calcul mai robuste decât cele disponibile cu procesoarele de uz general. În timp ce FPGA-urile sunt bine echipate pentru a îndeplini cerințele de performanță și de consum redus de energie ale execuției modelelor de inferență, metodele convenționale de dezvoltare a FPGA-urilor pot părea complexe, determinând adesea dezvoltatorii să aleagă soluții suboptime.

După cum s-a arătat, prin utilizarea IP-urilor și a software-ului specializat de la Microchip Technology, dezvoltatorii fără experiență în FPGA pot implementa proiecte bazate pe inferență, care sunt mai capabile să îndeplinească cerințele de performanță, putere, precum și cerințele de planificare a proiectării.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.