Utilizarea unui emițător-receptor RF agil într-un sistem de comunicații SDR adaptiv pentru industria aerospațială și de apărare

Contributed By DigiKey's North American Editors

2023-11-30

Proiectanții de sisteme din domeniul aerospațial și al apărării (ADEF) se confruntă cu o cerere neîncetată de sisteme de comunicații mai compacte și mai puțin consumatoare de energie, capabile să răspundă cu agilitate la un mediu de semnale dinamice. Depășind arhitecturile radio tradiționale, tehnologia radio definită prin software (SDR) poate contribui la îndeplinirea cerințelor în schimbare rapidă pentru radiourile ADEF, dar implementarea SDR a prezentat multiple provocări pentru îndeplinirea atât a cerințelor funcționale, cât și a nevoii de a reduce dimensiunea, greutatea și puterea (SWaP).

Acest articol descrie o soluție SDR mai eficientă de la Analog Devices, care poate simplifica proiectarea sistemelor de comunicații cu consum redus de energie, compacte și agile, fără a compromite performanța.

Provocările emergente determină cerințe mai exigente

Proiectanții se confruntă cu o cerere de comunicații mai eficiente într-un număr tot mai mare de aplicații industriale și esențiale, inclusiv comunicații radio securizate, radare adaptive, război electronic și navigație GPS îmbunătățită. Aceste noi provocări conduc la necesitatea unei funcționări îmbunătățite în bandă largă, a unei game dinamice mai mari, a unei mai mari agilități în ceea ce privește frecvențele și a capacității de reconfigurare. Totuși, aceste cerințe funcționale mai exigente pot intra în conflict cu necesitatea de a reduce SWaP pe măsură ce sistemele de comunicații se deplasează către platforme mai mici alimentate cu baterii, inclusiv vehicule aeriene fără pilot (UAS) și unități portabile.

Soluțiile de proiectare bazate pe arhitecturi radio superheterodine discrete tradiționale oferă performanțe ridicate, o gamă dinamică largă și un zgomot de fond minim. Pentru proiectanți, provocarea de a izola semnalul dorit de frecvența intermediară (IF), care se află în centrul acestei abordări, duce, de obicei, la proiecte complexe cu SWaP ridicat și capacitate de reconfigurare mică sau chiar fără această capacitate (Figura 1).

Figura 1: Arhitecturile radio tradiționale superheterodine pot îndeplini obiectivele de performanță, dar complexitatea lor le împiedică să îndeplinească obiectivele emergente pentru un SWaP minim. (Sursă imagine: Analog Devices)

Figura 1: Arhitecturile radio tradiționale superheterodine pot îndeplini obiectivele de performanță, dar complexitatea lor le împiedică să îndeplinească obiectivele emergente pentru un SWaP minim. (Sursă imagine: Analog Devices)

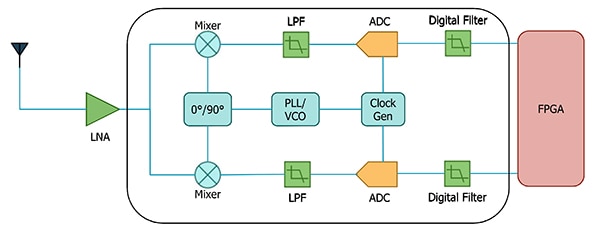

În schimb, arhitecturile de conversie directă (zero-IF) reduc atât cerințele de filtrare, cât și nevoia de convertoare analogice-digitale (ADC) cu lățime de bandă foarte mare, ceea ce duce la un design mai simplu care poate fi implementat pe un singur cip (Figura 2).

Figura 2: Arhitecturile radio zero-IF pot satisface nevoia de performanță mai mare și de SWaP mai mic, dar izolarea semnalului este o provocare. (Sursă imagine: Analog Devices)

Figura 2: Arhitecturile radio zero-IF pot satisface nevoia de performanță mai mare și de SWaP mai mic, dar izolarea semnalului este o provocare. (Sursă imagine: Analog Devices)

În ciuda avantajelor sale aparente, arhitectura cu conversie directă prezintă propriile provocări de implementare care au limitat adoptarea sa pe scară largă. În această arhitectură, semnalul este convertit într-o purtătoare de radiofrecvență (RF) la frecvența oscilatorului local (LO), dar erorile de decalaj în curent continuu (c.c.) și scurgerile LO pot duce la erori care se propagă prin lanțul de semnal. În plus, diferențele dintre traseele de semnal, chiar și în cadrul aceluiași cip, pot introduce o neconcordanță de câștig sau de fază a semnalului în fază (I) și în cuadratură (Q), ceea ce duce la o eroare de cuadratură care poate compromite izolarea semnalului.

Tehnologia SDR oferă potențialul de a depăși limitările arhitecturilor radio tradiționale, dar puține soluții pot aborda cerințele mai largi asociate cu aplicațiile ADEF. Utilizând emițătorul-receptorul RF ADRV9002 de la Analog Devices, dezvoltatorii pot îndeplini cu ușurință nevoia acestor aplicații de performanță și funcționalitate mai mare cu SWaP mai mic.

Funcționalitatea integrată oferă performanțe optimizate cu SWaP redus

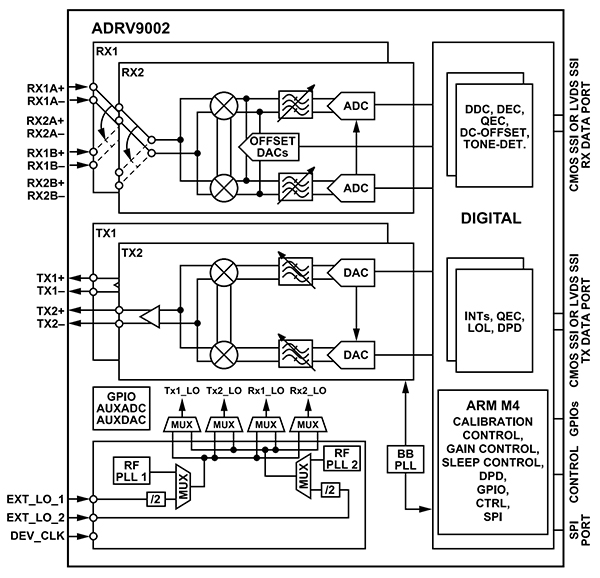

Suportând o gamă de frecvențe de la 30 megahertzi (MHz) la 6.000 MHz, ADRV9002 este un emițător-receptor foarte bine integrat care conține toate funcționalitățile RF, de semnal mixt și digitale necesare pentru a susține o gamă largă de cerințe pentru aplicații. Capabil să funcționeze atât în regim Time Division Duplex (TDD), cât și în regim Frequency Division Duplexi (FDD), dispozitivul dispune de subsisteme separate de receptor și emițător cu conversie directă pe două canale, care includ filtre digitale programabile, corecția decalajului c.c. și corecția erorilor în cuadratură (QEC).

În cadrul subsistemului sintetizatorului pe cip, ADRV9002 dispune de două căi distincte de buclă cu blocare de fază (PLL): una pentru calea RF de înaltă frecvență și alta pentru ceasurile digitale și ceasurile de eșantionare ale convertorului. În cele din urmă, blocul de procesare a semnalului digital al dispozitivului include un procesor încorporat Arm® M4 care gestionează funcțiile de autocalibrare și control (Figura 3).

Figura 3: Emițătorul-receptorul RF ADRV9002 integrează subsisteme duble de recepție (RX) și de transmisie (TX). (Sursă imagine: Analog Devices)

Figura 3: Emițătorul-receptorul RF ADRV9002 integrează subsisteme duble de recepție (RX) și de transmisie (TX). (Sursă imagine: Analog Devices)

Capabil să funcționeze fie în modul zero-IF, fie în modul low-IF pentru aplicații sensibile la zgomot de fază, ADRV9002 dispune de subsisteme de emițător și receptor care oferă lanțuri de semnal complete. Fiecare subsistem emițător oferă o pereche de convertoare digital-analogice (DAC), filtre și mixere care recombină semnalele I și Q și le modulează pe frecvența purtătoare pentru transmisie.

Fiecare subsistem receptor integrează o rețea de intrare rezistivă pentru controlul câștigului care alimentează un mixer pasiv în mod curent. La rândul său, un amplificator de transimpedanță convertește ieșirea de curent a mixerului la un nivel de tensiune care este digitizat de un ADC cu o gamă dinamică ridicată. În timpul intervalelor disponibile pentru emițător în funcționarea TDD sau în aplicațiile FDD în care se utilizează un singur sistem de recepție, intrările neutilizate ale receptorului pot fi utilizate pentru a monitoriza canalele emițătorului în ceea ce privește scurgerile LO și QEC, sau intrările neutilizate ale receptorului pot fi utilizate pentru a monitoriza nivelurile semnalului de ieșire ale amplificatorului de putere (PA).

Această ultimă capacitate intră în joc în funcția integrată de pre-distorsiune digitală (DPD) a ADRV9002, care utilizează nivelurile monitorizate ale semnalului PA pentru a aplica pre-distorsiunea adecvată necesară pentru a liniariza ieșirea. Această capacitate permite ADRV9002 să conducă amplificatorul de putere mai aproape de saturație, optimizându-i eficiența.

Reglarea puterii și a performanțelor

Dispozitivul ADRV9002 oferă o soluție complet integrată într-o matrice cu bile (BGA) și capsulă la nivel de cip (CSP) cu 196 de bile, minimizând dimensiunea și greutatea pentru sistemele de comunicații SDR ADEF. Pentru a-i ajuta pe dezvoltatori să optimizeze și mai mult consumul de energie, ADRV9002 integrează mai multe caracteristici concepute special pentru a-i ajuta pe dezvoltatori să găsească un echilibru adecvat între performanță și putere.

La nivel de bloc, dezvoltatorii pot implementa scalarea puterii pe blocuri individuale de traseu al semnalului pentru a schimba performanța redusă cu un consum mai mic de energie. În plus, blocurile din cadrele de recepție (RX) și de transmisie (TX) TDD pot fi dezactivate pentru a sacrifica timpii de întoarcere RX/TX sau TX/RX pentru un consum de energie mai mic. Pentru a ajuta și mai mult capacitatea dezvoltatorilor de a optimiza puterea în raport cu performanța, fiecare subsistem receptor ADRV9002 include două perechi de ADC-uri. O pereche cuprinde ADC-uri sigma-delta de înaltă performanță, în timp ce a doua pereche poate fi înlocuită atunci când consumul de energie este critic.

Pentru aplicații caracterizate de perioade de inactivitate, se poate utiliza modul de monitorizare RX al ADRV9002. În acest mod, ADRV9002 alternează între o stare de veghe cu putere minimă și o stare de detectare la un ciclu de funcționare programat. În starea de detectare, dispozitivul activează un receptor și încearcă să achiziționeze un semnal pe o lățime de bandă și o frecvență RX LO programate de dezvoltator. Dacă dispozitivul măsoară nivelul de putere al semnalului peste pragul programat, dispozitivul iese din modul de monitorizare, iar blocurile ADRV9002 sunt alimentate pentru a gestiona semnalul dorit.

Prototipare și dezvoltare rapide

Pentru a-i ajuta pe ingineri să treacă rapid la evaluare, prototipuri și dezvoltare, Analog Devices oferă suport hardware și software extins pentru sistemele bazate pe ADRV9002.

Pentru suportul hardware, Analog Devices oferă o pereche de plăci bazate pe ADRV9002:

- ADRV9002NP/W1/PCBZ pentru aplicații de bandă joasă care operează în intervalul de la 30 MHz la 3 gigahertzi (GHz)

- ADRV9002NP/W2/PCBZ pentru aplicații de bandă înaltă în gama 3-6 GHz

Echipate cu conectori FMC, aceste plăci acceptă ADRV9002 integrat cu reglarea puterii și interfețe hardware, precum și distribuția ceasului și a sincronizării cu cipuri multiple (MCS). Plăcile se conectează prin intermediul conectorului FMC la o placă de bază FPGA, cum ar fi placa de evaluare ZCU102 de la AMD, pentru alimentarea și controlul aplicației.

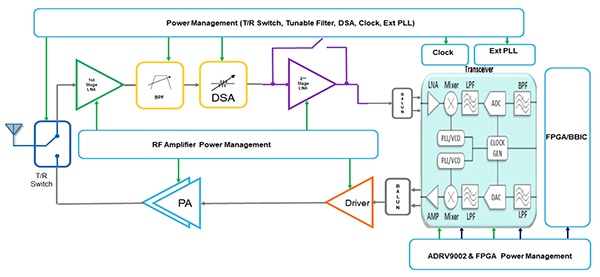

Analog Devices oferă o schemă completă și o listă de materiale (BOM) pentru plăcile radio ADRV9002NP în pachetul de asistență. Schema și lista de materiale oferă un punct de plecare eficient pentru dezvoltarea de hardware personalizat pentru majoritatea aplicațiilor. Unele aplicații necesită un front-end RF suplimentar pentru a îndeplini cerințele specifice de condiționare a semnalului. Pentru aceste aplicații, dezvoltatorii au nevoie doar de câteva componente suplimentare pentru a-și finaliza proiectul (Figura 4).

Figura 4: Emițătorul-receptorul cu grad ridicat de integrare ADRV9002 permite dezvoltatorilor să implementeze rapid proiecte specializate. (Sursă imagine: Analog Devices)

Figura 4: Emițătorul-receptorul cu grad ridicat de integrare ADRV9002 permite dezvoltatorilor să implementeze rapid proiecte specializate. (Sursă imagine: Analog Devices)

În acest exemplu, dezvoltatorii pot implementa rapid un front-end RF adecvat utilizând următoarele componente de gestionare a puterii de la Analog Devices:

- Comutator RF ADRF5160

- Amplificator de zgomot redus (LNA) HMC8411

- Filtru trece-bandă acordabil digital ADMV8526

- Atenuator RF digital în trepte (DSA) HMC1119

- Amplificator driver HMC8413

- PA HMC8205B

Analog Devices oferă suport complet pentru dezvoltarea de software prin intermediul documentației și al pachetelor de software descărcabile. Dezvoltatorii care utilizează hardware-ul de dezvoltare menționat mai sus pot continua cu prototiparea și dezvoltarea pe baza software-ului din gama de produse de la Analog Devices sau a pachetelor software open-source.

Acest articol limitează discuția de mai jos la programele software pentru gama de produse. Pentru mai multe informații despre metodologia de dezvoltare open-source, consultați Ghidul utilizatorului pentru platforma de prototipare ADRV9001/2 de la Analog Devices.Analog Devices precizează că termenul „ADRV9001” din documentația de suport a companiei este înțeles ca un indicativ de familie care include ADRV9002 și alți membri ai familiei ADRV9001. În consecință, trimiterile la ADRV9001 din textul sau figurile de mai jos se aplică dispozitivului ADRV9002, care face obiectul prezentului articol.

Disponibil prin intermediul distribuției kitului de dezvoltare software (SDK) al gamei de produse de la Analog Devices, instrumentul Transceiver Evaluation Software (TES) bazat pe Windows al companiei oferă un punct de plecare accesibil pentru configurarea și evaluarea rapidă a performanțelor emițătorului-receptorului.

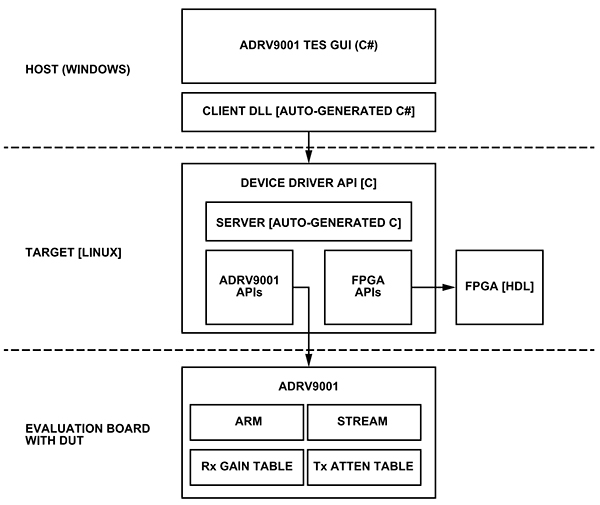

În timpul evaluării și prototipării cu plăcile bazate pe ADRV9002 de la Analog Devices și cu placa de evaluare ZCU102 de la AMD, instrumentul TES oferă o interfață grafică pentru utilizator (GUI) pentru configurarea hardware-ului și observarea datelor înregistrate (Figura 5).

Figura 5: Instrumentul TES din pachetul SDK permite dezvoltatorilor să înceapă rapid evaluarea emițătorului-receptorului ADRV9002 pe platforma de evaluare acceptată. (Sursă imagine: Analog Devices)

Figura 5: Instrumentul TES din pachetul SDK permite dezvoltatorilor să înceapă rapid evaluarea emițătorului-receptorului ADRV9002 pe platforma de evaluare acceptată. (Sursă imagine: Analog Devices)

La rândul său, instrumentul TES generează automat cod C# care poate fi compilat în mediul Linux, în mediul MATLAB sau în Python. SDK oferă un set complet de biblioteci software și interfețe de programare a aplicațiilor (API), inclusiv pachetul API ADRV9001 dezvoltat pentru platforma AMD ZCU102.

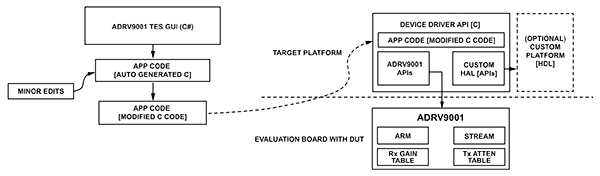

De asemenea, fluxul SDK sprijină direct migrarea de la evaluarea și prototiparea cu placa de evaluare la mediul țintă personalizat al dezvoltatorului (Figura 6).

Figura 6: Arhitectura SDK permite dezvoltatorilor să extindă cu ușurință rezultatele evaluării lor la propria platformă țintă. (Sursă imagine: Analog Devices)

Figura 6: Arhitectura SDK permite dezvoltatorilor să extindă cu ușurință rezultatele evaluării lor la propria platformă țintă. (Sursă imagine: Analog Devices)

În acest flux de migrare, dezvoltatorul lasă TES să autogenereze codul ca de obicei. Cu toate acestea, în loc să îl utilizeze direct, dezvoltatorul implementează o versiune editată a codului generat pe platforma țintă. În practică, modificările necesare se limitează în principal la eliminarea apelurilor de funcții care fac trimitere la componente hardware recunoscute de instrumentul TES, dar care nu sunt necesare în sistemul țintă. Arhitectura SDK include o interfață pentru stratul de abstractizare hardware (HAL) între biblioteca ADRV9001 și hardware-ul dezvoltatorilor, astfel încât dezvoltatorii trebuie doar să furnizeze cod personalizat care să implementeze codul de interfață HAL pentru hardware-ul lor specific. Prin urmare, dezvoltatorii pot trece rapid de la evaluarea cu ajutorul plăcilor de la Analog Devices și a plăcii AMD la dezvoltarea pentru mediul lor țintă personalizat.

Concluzie

Aplicațiile ADEF se confruntă cu provocări din ce în ce mai mari într-un mediu de semnale din ce în ce mai complexe. Pe lângă satisfacerea cererii de performanțe mai ridicate pe o gamă mai largă de frecvențe, dezvoltatorii trebuie să reducă SWaP pentru a sprijini migrarea acestor aplicații către sisteme alimentate cu baterii. Utilizând un emițător-receptor cu grad ridicat de integrare de la Analog Devices, dezvoltatorii pot implementa soluții SDR pentru a răspunde mai eficient acestor cerințe.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.