Elementele fundamentale ale sintetizatoarelor de frecvență cu buclă blocată în fază

Contributed By DigiKey's North American Editors

2021-02-03

Ratele de date din ce în ce mai mari în magistralele de comunicații de mare viteză în serie necesită semnale de tact de sistem cu frecvențe mai mari, stabilitate superioară, o rezoluție mai mare a frecvenței și o puritate mai mare a semnalului. Sintetizatoarele digitale directe oferă aceste caracteristici, dar numai la frecvențe sub 2 sau 3 gigahertzi (GHz). Este nevoie de găsirea unei soluții pentru frecvențe de până la zeci de gigahertzi.

Această soluție începe cu sintetizatoare de frecvență analogice pe bază de buclă blocată în fază (PLL) care generează frecvențe de tact de până la 30 GHz. Apoi, sintetizatoarele cu N întreg (care multiplică frecvența de referință cu o valoare întreagă) și sintetizatoarele cu N fracționar (care multiplică frecvența de referință cu valori fracționare neîntregi) utilizează tehnici speciale care minimizează zgomotul de fază și impuritățile similare ale semnalului.

Acest articol descrie proiectarea sintetizatoarelor de frecvență atât cu N întreg, cât și cu N fracționar, folosind ca exemplu dispozitive de la Analog Devices. Articolul evidențiază și inovațiile care permit utilizarea acestor dispozitive pentru legături seriale de date de mare viteză, precum și pentru radare cu frecvență agilă.

Sintetizatoare N întreg cu buclă blocată în fază

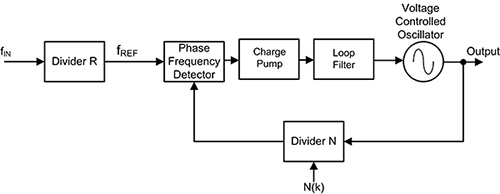

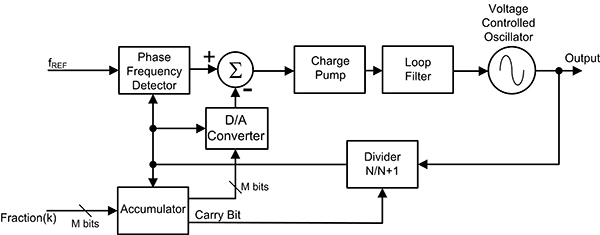

Circuitele PLL sunt utilizate pentru controlul frecvenței și al fazei. Acestea pot fi configurate ca surse de tact, multiplicatoare de frecvență, demodulatoare, generatoare de urmărire sau circuite de recuperare a ceasului. Fiecare dintre aceste aplicații necesită caracteristici diferite, dar toate utilizează același concept de circuit de bază. Figura 1 prezintă o schemă bloc a unui PLL de bază configurat ca multiplicator de frecvență.

Figura 1: schema bloc a unui sintetizator de frecvență clasic N întreg cu buclă blocată în fază. (Sursă imagine: DigiKey)

Figura 1: schema bloc a unui sintetizator de frecvență clasic N întreg cu buclă blocată în fază. (Sursă imagine: DigiKey)

Funcționarea acestui circuit este tipică pentru toate buclele blocate în fază. Practic, acesta este un sistem de control al feedback-ului care controlează faza unui oscilator comandat în tensiune (VCO). Semnalul de intrare este aplicat unui divizor de pre-scalare, care împarte frecvența de intrare la un factor R. Ieșirea dispozitivului de pre-scalare este frecvența de referință, care formează una dintre intrările unui detector de fază-frecvență (PFD).

Cealaltă intrare PFD este un semnal de feedback de la ieșirea unui contor cu împărțire la N. În mod normal, dacă PLL este blocat, frecvențele ambelor semnale vor fi aproape identice. Ieșirea detectorului de fază este o tensiune proporțională cu diferența de fază dintre cele două intrări. Dacă bucla este deblocată, așa cum se întâmplă la pornire, sau dacă există o deplasare mare instantanee a frecvenței de intrare, atunci detectorul de fază-frecvență funcționează pentru a direcționa frecvența de funcționare PLL la setarea dorită. Atunci când se atinge frecvența respectivă, PFD revine la modul detector de fază și are o ieșire proporțională cu diferența de fază dintre frecvența de referință și semnalul de feedback.

Detectorul de fază-frecvență acționează o pompă de sarcină, care este o sursă de curent comutată bipolar. Acest lucru înseamnă că poate emite impulsuri de curent pozitive și negative în filtrul de buclă al PLL.

Filtrul de buclă netezește semnalul de eroare de fază și determină și caracteristicile dinamice ale PLL. Semnalul filtrat controlează VCO. Rețineți că ieșirea VCO este la o frecvență care este de N ori mai mare decât intrarea furnizată la intrarea de referință de frecvență a detectorului de fază-frecvență și de N/R ori mai mare decât intrarea de frecvență. Acest semnal de ieșire este trimis înapoi la detectorul de fază prin intermediul contorului cu împărțire la N.

În mod normal, filtrul de buclă este conceput pentru a se potrivi cu caracteristicile solicitate de aplicația PLL. În cazul în care PLL trebuie să captureze și să urmărească un semnal, lățimea de bandă a filtrului de buclă va fi mai mare decât ar fi fost dacă s-ar fi așteptat o frecvență de intrare fixă. Intervalul de frecvențe pe care PLL îl va accepta și pe care se va bloca se numește „intervalul de capturare”. Odată ce PLL este blocat și urmărește un semnal, intervalul de frecvențe pe care PLL îl va urmări se numește „interval de urmărire”. În general, intervalul de urmărire este mai mare decât intervalul de capturare. De asemenea, filtrul de buclă PLL determină cât de repede se poate schimba frecvența semnalului și să se mențină blocarea – adică, viteza maximă de salt. Cu cât este mai îngustă lățimea de bandă a filtrului de buclă, cu atât este mai mică eroarea de fază care poate fi atinsă. Acest lucru vine cu dezavantajul unui răspuns mai lent și al unui interval redus de capturare. PLL-urile utilizate în aplicațiile pentru tact funcționează în principal la frecvențe fixe. În general, lățimea de bandă a filtrului de buclă trebuie să fie mult mai mică decât frecvența de referință.

Deoarece frecvența de ieșire PLL este un multiplu întreg al frecvenței de referință, rezoluția de frecvență al acestuia este egală cu frecvența de referință. Obținerea unei rezoluții mai fine a frecvenței necesită reducerea frecvenței de referință, ceea ce se obține cu ajutorul contorului dispozitivului de pre-scalare R.

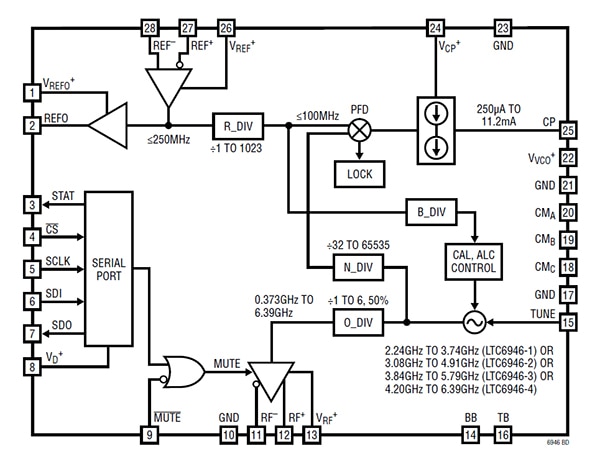

Un exemplu comercial al unui sintetizator de frecvență cu N întreg este LTC6946IUFD-3#PBF de la Analog Devices, un sintetizator cu zgomot redus, de la 0,64 la 5,790 GHz, cu un VCO integrat și performanțe excelente în ceea ce privește frecvențele parazite (Figura 2). Acesta face parte dintr-o familie de patru circuite integrate pentru sintetizatoare, fiecare cu o gamă de frecvențe diferită, acoperind o gamă totală cuprinsă între 0,373 și 6,390 GHz.

Figura 2: Schema bloc a sintetizatorului de frecvență cu N întreg LTC6946IUFD-3#PBF de la Analog Devices cu VCO integrat. (Sursă imagine: Analog Devices)

Figura 2: Schema bloc a sintetizatorului de frecvență cu N întreg LTC6946IUFD-3#PBF de la Analog Devices cu VCO integrat. (Sursă imagine: Analog Devices)

Acest sintetizator necesită un filtru de buclă extern furnizat de utilizator, care poate fi optimizat pentru o aplicație specifică. Există un divizor de contor intern cu pre-scalare, cu un interval de divizare de la 1 la 1023. Divizorul de buclă are un interval cuprins între 32 și 65535. Curentul pompei de sarcină poate fi reglat de la 250 microamperi (mA) la 11,2 miliamperi (mA) pentru a corespunde cerințelor filtrului de buclă.

Sintetizatoare N fracționar cu buclă blocată în fază

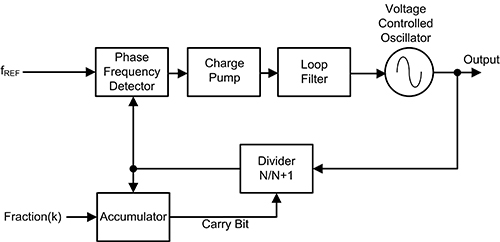

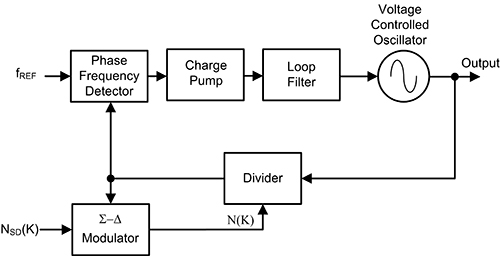

Rezoluția de frecvență a sintetizatorului PLL poate fi îmbunătățită prin reducerea mărimii pasului la valori mai mici decât cele întregi, adică prin efectuarea pașilor fracționari în divizorul de buclă (N). Acest lucru este realizat prin variația dinamică sau prin fenomenul de „dithering” al valorii numărătorii inverse. Asta înseamnă că setarea divizorului menține valoarea N pentru un număr fix de cicluri ale frecvenței de ieșire PLL și este trecută periodic la o valoare diferită, cum ar fi N+1. De exemplu, dacă setarea divizorului este 4 pentru trei perioade de referință și 5 pentru al patrulea ciclu de referință, atunci numărătoarea inversă efectivă este 4,25. O modalitate de a realiza acest lucru este utilizarea unui acumulator, după cum se arată în Figura 3.

Figura 3: Schema bloc a unui sintetizator PLL N fracționar care utilizează un acumulator pentru modularea numărului divizorului. (Sursă imagine: DigiKey)

Figura 3: Schema bloc a unui sintetizator PLL N fracționar care utilizează un acumulator pentru modularea numărului divizorului. (Sursă imagine: DigiKey)

Acumulatorul numără impulsurile de ieșire de la divizor, iar la fiecare M, unde M este modulul acumulatorului, emite un bit de transport care modifică intrarea divizorului. Figura 4 continuă exemplul de stabilire a unei setări a divizorului fracționar de 4,25.

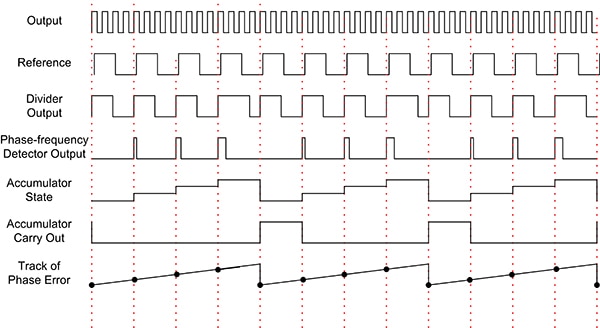

Figura 4: Schema de sincronizare a unui sintetizator N fracționar care utilizează un acumulator. (Sursă imagine: DigiKey)

Figura 4: Schema de sincronizare a unui sintetizator N fracționar care utilizează un acumulator. (Sursă imagine: DigiKey)

Acumulatorul este acționat de la ieșirea divizată și numără modulul patru, adică M este egal cu patru. La fiecare al patrulea impuls, acesta generează o ieșire de transport, care mărește cu unu numărul divizorului. Acumulatorul se resetează și începe să numere din nou. Creșterea setării divizorului deplasează frecvența de ieșire, ceea ce duce la o eroare acumulată a decalajului de fază. Urmărirea erorii de fază prezintă valoarea impulsului ca funcție de timp.

Setarea medie a divizorului este de 4,25, dar ieșirea sintetizatorului este modulată în fază, ceea ce duce la apariția unor tonuri false la ieșire. Dacă ne uităm la starea acumulatorului, este evident că acesta urmărește eroarea de fază. Aceasta poate fi utilizată pentru a elimina modulația, după cum se arată în Figura 5.

Figura 5: utilizarea stării acumulatorului convertit D/A pentru anularea modulației de fază datorate fenomenului de dithering N fracționar. (Sursă imagine: DigiKey)

Figura 5: utilizarea stării acumulatorului convertit D/A pentru anularea modulației de fază datorate fenomenului de dithering N fracționar. (Sursă imagine: DigiKey)

Starea acumulatorului este convertită în semnal analogic de către un convertor digital-analogic (D/A) și este scalată și scăzută din ieșirea detectorului de fază-frecvență pentru a anula modulația de fază cauzată de fenomenul de dithering N fracționar. Acest lucru trebuie realizat cu mare atenție; dacă semnalul de corecție nu se potrivește exact cu eroarea de fază, atunci vor rezulta tonuri false la ieșire.

Intră în scenă modulatorul sigma-delta

Periodicitatea acumulatorului cauzează ieșiri false de la sintetizator. Dacă acumulatorul este înlocuit cu un modulator sigma-delta, atunci se pot aplica tehnici digitale pentru a modula numărul divizorului astfel încât să se reducă la minimum răspunsurile false și zgomotul. Această înlocuire este prezentată în Figura 6.

Figura 6: înlocuirea acumulatorului cu un modulator sigma-delta permite aplicarea tehnicilor digitale pentru varierea numărului divizorului în vederea reducerii răspunsurilor false. (Sursă imagine: DigiKey)

Figura 6: înlocuirea acumulatorului cu un modulator sigma-delta permite aplicarea tehnicilor digitale pentru varierea numărului divizorului în vederea reducerii răspunsurilor false. (Sursă imagine: DigiKey)

Există într-adevăr două tehnici digitale comune care sunt utilizate în topologia de modulare sigma-delta. Prima implică creșterea numărului divizorului N într-o gamă mai amplă de valori, astfel ca factorul mediu de divizare să producă valoarea fracționară dorită a divizorului. Acest lucru va reduce impulsurile fracționare principale. Sintetizatorul pe bază de acumulator variază numărătoarea între două stări. Aceasta este o metodă de modulație de ordinul întâi. Un PLL fracționar sigma-delta de ordinul n modulează contorul N între 2n valori diferite. De exemplu, un modulator de ordinul al treilea ar alterna între opt valori diferite ale divizorului, iar un modulator de ordinul al patrulea ar alterna între 16 valori diferite ale divizorului.

A doua tehnică digitală – denumită și dithering – implică randomizarea secvenței 2N astfel ca aceasta să fie pseudoaleatoare. Menținând în continuare un raport mediu al divizorului fracționar, acesta convertește impulsurile fracționare în zgomot de formă aleatoriu, astfel încât să poată fi filtrat de PLL.

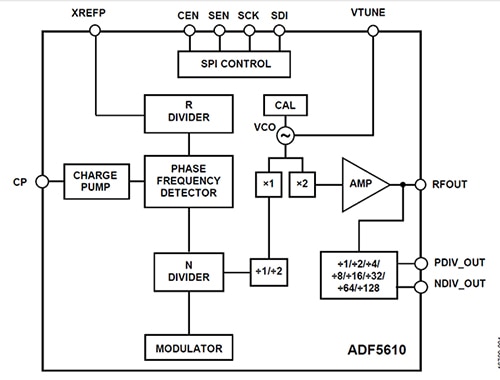

O versiune comercială a unui sintetizator sigma-delta N fracționar este ADF5610BCCZ Analog Devices, un sintetizator N fracționar cu zgomot redus, de la 0,57 megahertzi (MHz) la 14,6 GHz, cu un VCO integrat (Figura 7).

Figura 7: o schemă bloc a dispozitivului ADF5610BCCZ Analog Devices care acceptă atât configurații de sintetizator N fracționar, cât și întreg. (Sursă imagine: Analog Devices)

Figura 7: o schemă bloc a dispozitivului ADF5610BCCZ Analog Devices care acceptă atât configurații de sintetizator N fracționar, cât și întreg. (Sursă imagine: Analog Devices)

ADF5610 necesită un oscilator de referință extern și un filtru de buclă. Acesta are un VCO integrat cu o frecvență fundamentală de 3650 MHz până la 7300 MHz. Aceste frecvențe sunt dublate intern și direcționate către pinul RFOUT. Există o ieșire diferențială care permite ca frecvența VCO dublată să fie împărțită la factori de 1, 2, 4, 8, 16, 32, 64 sau 128, ceea ce permite generarea de frecvențe de ieșire RF de până la 57 MHz.

ADF5610 utilizează un modulator sigma-delta avansat cu un modul fracționar pe 24 de biți care atinge niveluri aparente excepțional de scăzute. La fel ca în cazul tuturor sintetizatoarelor care utilizează un modulator sigma-delta, acest dispozitiv utilizează tehnici de procesare a semnalelor digitale pentru a găsi raportul mediu dorit al divizorului fracționar. Acest proces, sincronizat la rata PFD, produce un zgomot de modulație de ieșire numit zgomot de cuantificare, cu un răspuns în frecvență înaltă. Filtrul extern de buclă trece-jos este utilizat pentru a filtra acest zgomot de cuantificare la un nivel sub zgomotul de fază al VCO, împiedicând astfel ca zgomotul să contribuie la zgomotul de fază general al sistemului.

De asemenea, ADF5610 include și un mod de frecvență exactă pentru o eroare de frecvență de 0 hertzi (Hz). Acest mod poate genera frecvențe exacte între pașii limită adiacenți pentru N întreg, utilizând în același timp modulul complet al acumulatorului de fază pe 24 de biți. Acesta realizează pași de frecvență exacți cu o rată mare de comparare a detectorului de fază, permițând astfel PLL-ului să mențină o performanță excelentă a zgomotului de fază și a zgomotului fals.

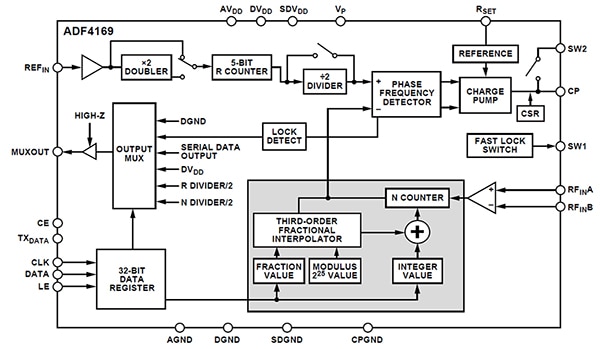

ADF4169CCPZ-RL7 de la Analog Devices este un alt sintetizator PLL care poate fi configurat fie ca un dispozitiv N întreg, fie ca un dispozitiv N fracționar. Acesta funcționează cu o lățime de bandă RF de până la 13,5 GHz cu modulație și generare de forme de undă. Sintetizatorul utilizează o intrare de frecvență de referință externă, un VCO și un filtru de buclă. Acesta are un modulator sigma-delta de ordinul al treilea pentru sinteza N fracționar care poate fi dezactivat, permițând dispozitivului să funcționeze în modul N întreg (Figura 8).

Figura 8: ADF4169CCPZ-RL7 Analog Devices utilizează un modulator sigma-delta de ordinul al treilea. (Sursă imagine: Analog Devices)

Figura 8: ADF4169CCPZ-RL7 Analog Devices utilizează un modulator sigma-delta de ordinul al treilea. (Sursă imagine: Analog Devices)

Sintetizatorul ADF4158WCCPZ-RL7 este destinat utilizării în radarele cu unde continue modulate în frecvență (FMCW). Acesta este capabil să realizeze diferite tipuri de forme de undă modulate în domeniul frecvenței, inclusiv rampe cu formă de dinți de fierăstrău și triunghiulare. Aceasta este o caracteristică specială, necesară în aplicațiile radar.

Concluzie

Ratele de date din ce în ce mai mari în magistralele de comunicații de mare viteză în serie impun proiectanților să caute soluții de tact de sistem dincolo de sintetizatoarele digitale directe – care funcționează cel mai bine sub 3 GHz. Sintetizatoarele de frecvență bazate pe PLL care utilizează topologii N întreg și N fracționar oferă semnale stabile, cu zgomot redus pentru tact de înaltă frecvență, comunicații de date în serie și aplicații radar pentru frecvențe de până la zeci de gigahertzi.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.