Arhitectura coprocesorului: o arhitectură a sistemului încorporat pentru prototipare rapidă

2021-07-06

Nota editorului – Chiar dacă este binecunoscută pentru performanța și capacitatea sa de procesare digitală, arhitectura coprocesorului oferă proiectantului de sisteme integrate oportunități de implementare a strategiilor de management al proiectelor, care îmbunătățesc atât costurile de dezvoltare, cât și timpul de lansare pe piață. Acest articol, care se concentrează, în special, pe combinația dintre un microcontroler discret (MCU) și o rețea de porți programabile în câmp (FPGA), prezintă modul în care această arhitectură se pretează la un proces de proiectare eficient și iterativ. Folosind surse documentate, constatări empirice și studii de caz, sunt explorate beneficiile acestei arhitecturi și sunt oferite aplicații tipice. La finalul acestui articol, proiectantul de sisteme integrate va înțelege mai bine când și cum trebuie să implementeze această arhitectură hardware versatilă.

Introducere

Proiectantul sistemelor încorporate se confruntă cu o serie de provocări legate de constrângerile impuse de proiectare, de așteptările legate de performanță și de preocupările legate de program și buget. Într-adevăr, chiar și contradicțiile din frazele și cuvintele-cheie utilizate în managementul modern al proiectelor subliniază și mai mult natura precară a acestui rol: „raportează rapid defecțiunile”; „fii agil”; „garantează siguranța pentru viitor”; și „fii disruptiv!”. Acrobațiile implicate chiar și în încercarea de a satisface aceste așteptări pot fi chinuitoare și, cu toate acestea, s-a vorbit despre ele și acestea continuă să fie consolidate pe piață. Este nevoie de o abordare de proiectare care să permită implementarea unui proces iterativ evolutiv și, la fel ca în cazul majorității sistemelor integrate, acesta începe cu arhitectura hardware.

Arhitectura coprocesoarelor, o arhitectură hardware cunoscută pentru faptul că îmbină punctele forte ale tehnologiilor microcontrolerului (MCU) și rețelei de porți programabile în câmp (FPGA), poate oferi proiectantului de sisteme integrate un proces capabil să îndeplinească chiar și cele mai exigente cerințe, permițând, totodată, flexibilitatea necesară pentru a aborda atât provocările cunoscute, cât și provocările necunoscute. Prin furnizarea de hardware capabil să se adapteze iterativ, proiectantul poate demonstra progresul, poate atinge etape-cheie critice și poate profita pe deplin de procesul de prototipare rapidă.

În cadrul acestui proces există etape-cheie ale proiectului, fiecare dintre acestea având valoarea sa unică pe care o adaugă efortului de dezvoltare. Pe parcursul acestui articol, se va face trimitere la acestea prin intermediul următorilor termeni: etapa-cheie de Procesare digitală a semnalelor cu ajutorul microcontrolerului, etapa-cheie de Gestionare a sistemului cu ajutorul microcontrolerului și etapa-cheie de Implementare a produsului.

Până la încheierea acestui articol, vom demonstra că o arhitectură hardware flexibilă poate fi mai adecvată pentru proiectarea sistemelor integrate moderne decât o abordare mai rigidă. În plus, această abordare poate aduce îmbunătățiri atât în ceea ce privește costul proiectului, cât și timpul de lansare pe piață. Argumentele, exemplele furnizate și studiile de caz vor fi folosite în apărarea acestei afirmații. Observând valoarea fiecărei etape-cheie în cadrul flexibilității proiectării oferite de această arhitectură, devine clar că o arhitectură hardware adaptivă este un motor puternic pentru avansarea proiectării sistemelor încorporate.

Explorarea punctelor forte ale arhitecturii coprocesorului: flexibilitate în proiectare și procesare de înaltă performanță

O aplicație obișnuită pentru proiectele FPGA este crearea unei interfețe directe cu un convertor analog-digital de mare viteză (ADC). Semnalul este digitalizat, citit în FPGA, iar apoi acestui semnal i se aplică algoritmi de procesare a semnalelor digitale (DSP). În cele din urmă, FPGA ia decizii pe baza constatărilor.

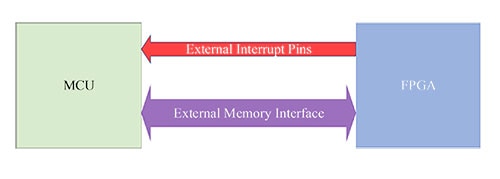

O astfel de aplicație va servi drept exemplu pe parcursul acestui articol. În plus, Figura 1 ilustrează o arhitectură generică a coprocesorului, în care MCU și FPGA sunt conectate prin intermediul interfeței de memorie externă a MCU. FPGA este tratată ca și cum ar fi un fragment de memorie statică externă cu acces aleatoriu (SRAM). Semnalele se întorc la MCU de la FPGA și servesc drept linii de întrerupere hardware și indicatori de stare. Acest lucru îi permite FPGA să ofere microcontrolerului MCU indicații despre stările critice, de exemplu să îi comunice că este pregătită o conversie ADC sau că a survenit o eroare sau că s-a produs un alt eveniment demn de remarcat.

Figura 1: Diagrama generică a coprocesorului (MCU + FPGA). (Sursă imagine: CEPD)

Figura 1: Diagrama generică a coprocesorului (MCU + FPGA). (Sursă imagine: CEPD)

Punctele forte ale abordării bazate pe coprocesor sunt, probabil, cel mai bine evidențiate în cadrul rezultatelor obținute în fiecare dintre etapele-cheie menționate mai sus. Valoarea este evaluată nu doar prin enumerarea realizărilor unei sarcini sau faze, ci și prin evaluarea capacității de activare pe care aceste realizări o permit. Răspunsurile la următoarele întrebări ajută la evaluarea valorii globale a rezultatelor obținute în cadrul unei etape-cheie:

- Pot continua acum mai rapid progresele celorlalți membri ai echipei, pe măsură ce sunt eliminate dependențele și blocajele din proiect?

- Cum permit realizările din această etapă-cheie alte căi de execuție paralelă?

Etapa-cheie de procesare digitală a semnalelor cu ajutorul microcontrolerului

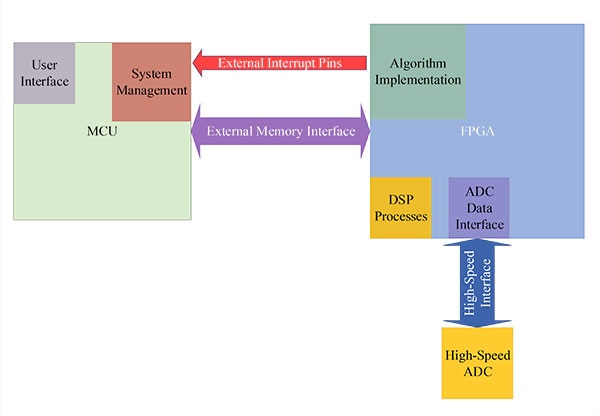

Figura 2: Arhitectură – procesare digitală a semnalelor cu ajutorul microcontrolerului. (Sursă imagine: CEPD)

Figura 2: Arhitectură – procesare digitală a semnalelor cu ajutorul microcontrolerului. (Sursă imagine: CEPD)

Prima etapă de dezvoltare pe care o permite această arhitectură hardware plasează MCU în față și în centru. În condiții normale, dezvoltarea MCU și a software-ului executabil necesită mai puține resurse și mai puțin timp decât dezvoltarea FPGA și a limbajului descriptiv hardware (HDL). Astfel, prin inițierea dezvoltării produsului cu MCU ca procesor principal, algoritmii pot fi implementați, testați și validați mai rapid. Acest lucru permite descoperirea erorilor algoritmice și logice încă din faza incipientă a procesului de proiectare și permite, de asemenea, testarea și validarea unor porțiuni importante din lanțul de semnal.

Rolul FPGA în această etapă-cheie inițială este de a servi drept interfață de colectare a datelor de mare viteză. Sarcina sa este de a transmite în mod fiabil datele de la ADC-ul de mare viteză, de a alerta MCU că datele sunt disponibile și de a prezenta aceste date pe interfața de memorie externă a MCU. Deși acest rol nu include implementarea proceselor DSP bazate pe HDL sau a altor algoritmi, acesta este, totuși, extrem de important.

Dezvoltarea FPGA realizată în această fază pune bazele succesului final al produsului, atât în cadrul eforturilor de dezvoltare a produsului, cât și de lansare pe piață. Atenția fiind concentrată doar pe interfața de nivel scăzut, se poate dedica timp suficient pentru testarea acestor operațiuni esențiale. Numai după ce FPGA îndeplinește în mod fiabil și sigur acest rol de interfață, această etapă-cheie poate fi încheiată cu încredere.

Rezultatele-cheie ale acestei etape-cheie inițiale includ următoarele beneficii:

- Întregul traseu al semnalului – toate amplificările, atenuările și conversiile – va fi testat și validat.

- Timpul și efortul depuse pentru dezvoltarea proiectului au fost reduse prin implementarea inițială a algoritmilor în software (C/C++); acest lucru are o valoare considerabilă pentru management și pentru alte părți interesate, care trebuie să vadă fezabilitatea acestui proiect înainte de a aproba fazele viitoare de proiectare.

- Lecțiile învățate din implementarea algoritmilor în C/C++ vor putea fi transferate direct la implementările HDL – prin utilizarea instrumentelor software-HDL, de ex., Xilinx HLS.

Etapa-cheie de gestionare a sistemului cu ajutorul microcontrolerului

Figura 3: Gestionarea sistemului cu ajutorul microcontrolerului. (Sursă imagine: CEPD)

Figura 3: Gestionarea sistemului cu ajutorul microcontrolerului. (Sursă imagine: CEPD)

A doua etapă de dezvoltare, oferită de această abordare a coprocesorului, este definită prin mutarea proceselor DSP și a implementărilor de algoritmi de la MCU la FPGA. Circuitul FPGA continuă să rămână responsabil pentru interfața ADC de mare viteză, însă, prin asumarea acestor alte roluri, viteza și paralelismul oferite de FPGA sunt utilizate pe deplin. În plus, spre deosebire de MCU, mai multe instanțe ale proceselor DSP și ale canalelor de algoritmi pot fi implementate și rulate simultan.

Bazându-se pe lecția învățată în urma implementării MCU, proiectantul își păstrează această încredere și în următoarea etapă-cheie. Instrumente precum Vivado HLS de la Xilinx, menționat mai sus, oferă o translație funcțională din codul C/C++ executabil în HDL sintetizabil. Acum, constrângerile de ordin temporal, parametrii procesului și alte preferințe ale utilizatorului trebuie definite și implementate în continuare, însă funcționalitatea de bază este păstrată și transpusă în structura FPGA.

Pentru această etapă-cheie, rolul MCU este acela de manager de sistem. Registrele de stare și de control din cadrul FPGA sunt monitorizate, actualizate și raportate de către MCU. În plus, MCU gestionează interfața cu utilizatorul (UI). Această interfață cu utilizatorul ar putea lua forma unui server web accesat prin intermediul unei conexiuni Ethernet sau Wi-Fi sau ar putea fi o interfață industrială cu ecran tactil care să ofere utilizatorilor acces la punctul de utilizare. Principala concluzie care se desprinde din noul rol mai rafinat al MCU este următoarea: pentru că au fost scutite de sarcinile de procesare intensivă, atât MCU, cât și FPGA sunt utilizate acum pentru sarcinile pentru care sunt foarte adecvate.

Rezultatele cheie ale acestei etape-cheie includ următoarele beneficii:

- Execuția rapidă și paralelă a proceselor DSP și a implementărilor de algoritmi este asigurată de FPGA.MCU oferă o interfață cu utilizatorul receptivă și simplificată și gestionează procesele produsului.

- După ce, mai întâi, au fost dezvoltate și validate în cadrul MCU, riscurile algoritmice au fost atenuate, iar aceste atenuări sunt transpuse în HDL-ul sintetizabil. Instrumente precum Vivado HLS, fac ca această translație să devină un proces mai ușor. În plus, riscurile specifice FPGA pot fi atenuate prin instrumente de simulare integrate, cum ar fi suita de proiectare Vivado.

- Părțile interesate nu sunt expuse unor riscuri semnificative prin mutarea proceselor pe FPGA. Dimpotrivă, acestea au ocazia să constate și să se bucure de avantajele pe care le oferă viteza și paralelismul FPGA. Sunt observate îmbunătățiri măsurabile ale performanței și acum se poate pune accentul pe pregătirea acestui proiect pentru producție.

Etapa-cheie de implementare a produsului

Având în vedere că procesarea intensivă din punct de vedere computațional este realizată în cadrul FPGA, iar MCU se ocupă de gestionarea sistemului și de rolurile interfeței cu utilizatorul, produsul este gata de implementare. Acum, acest document nu pledează pentru ocolirea versiunilor Alpha și Beta; cu toate acestea, în cadrul acestei etape-cheie, accentul este pus pe capacitățile pe care arhitectura coprocesorului le oferă pentru implementarea produsului.

Atât MCU, cât și FPGA sunt dispozitive care pot fi actualizate pe teren. S-au înregistrat mai multe progrese, astfel încât actualizările FPGA au devenit la fel de accesibile ca actualizările de software. În plus, deoarece FPGA se află în spațiul de memorie adresabil al MCU, MCU poate servi drept punct de acces pentru întregul sistem: primește atât actualizări pentru sine, cât și pentru FPGA. Actualizările pot fi programate condiționat, distribuite și personalizate în funcție de fiecare utilizator final. În cele din urmă, jurnalele utilizatorilor și ale cazurilor de utilizare pot fi păstrate și asociate cu implementările specifice de construcție. Din aceste seturi de date, performanța poate continua să fie rafinată și îmbunătățită chiar și după ce produsul este instalat pe teren.

Poate că punctele forte ale acestei posibilități de actualizare a întregului sistem nu sunt nicăieri mai importante decât în aplicațiile spațiale. Odată ce un produs este lansat, întreținerea și actualizările trebuie să fie efectuate de la distanță. Acest lucru poate fi la fel de simplu ca modificarea condițiilor logice sau la fel de complicat ca actualizarea unei scheme de modulație a comunicațiilor. Programabilitatea oferită de tehnologiile FPGA și de arhitectura coprocesorului poate găzdui întreaga gamă de capabilități, oferind, în același timp, opțiuni de componente rezistente la radiații.

Ultimul element-cheie din cadrul acestei etape-cheie este reducerea progresivă a costurilor. De asemenea, în această etapă-cheie pot avea loc reduceri de costuri, modificări ale listei de materiale (BOM) și alte optimizări. În timpul implementărilor de pe teren, se poate descoperi că produsul poate funcționa la fel de bine cu un MCU mai puțin costisitor sau cu un FPGA mai puțin capabil. Datorită coprocesorului, proiectanții de arhitectură nu sunt blocați în utilizarea unor componente ale căror capacități depășesc nevoile aplicației lor. În plus, în cazul în care o componentă devine indisponibilă, arhitectura permite integrarea de noi componente în proiect. Acest lucru nu este valabil în cazul unei arhitecturi cu un singur cip, al unui sistem pe un cip (SoC) sau al unui DSP sau MCU de înaltă performanță care încearcă să se ocupe de întreaga procesare a produsului. Arhitectura coprocesorului este o combinație bună între capacitate și flexibilitate, oferind proiectantului mai multe opțiuni și libertăți atât în fazele de dezvoltare, cât și de lansare pe piață.

Susținerea cercetării și studii de caz conexe

Exemplu de comunicații prin satelit

Pe scurt, valoarea unui coprocesor este de a descărca unitatea de procesare primară, astfel încât sarcinile să fie executate pe hardware, unde se poate profita de accelerări și simplificări. Avantajul unei astfel de alegeri de proiectare este o creștere netă a vitezei și a capacităților de calcul și, după cum se argumentează în acest articol, o reducere a costurilor și a timpului de dezvoltare. Poate că unul dintre cele mai convingătoare domenii în care aceste beneficii sunt posibile este cel al sistemelor de comunicații spațiale.

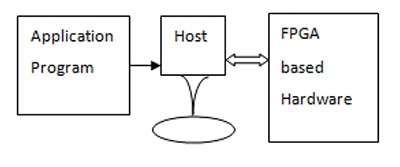

În lucrarea publicată de G. Prasad și N. Vasantha, intitulată FPGA based hardware as coprocessor, se detaliază modul în care procesarea datelor în cadrul unui FPGA îmbină nevoile de calcul ale sistemelor de comunicații prin satelit, fără costurile ridicate de inginerie nerecurente (NRE) ale circuitelor integrate specifice aplicației (ASIC) sau limitările specifice aplicației unui procesor cu arhitectură dură. Așa cum a fost descrisă în etapa-cheie de Procesare digitală a semnalelor cu ajutorul microcontrolerului, proiectarea acestora începe cu procesorul de aplicații care realizează majoritatea algoritmilor cu calcul intensiv. De la acest punct de plecare, aceștia identifică secțiunile-cheie ale software-ului care consumă majoritatea ciclurilor de ceas ale unității centrale de procesare (CPU) și migrează aceste secțiuni către implementarea HDL. Reprezentarea grafică este foarte asemănătoare cu cea prezentată până acum, însă aceștia au ales să reprezinte programul de aplicație ca un bloc independent, acesta putând fi realizat fie în gazdă (procesor), fie în hardware-ul bazat pe FPGA.

Figura 4: Program de aplicație, procesor gazdă și hardware bazat pe FPGA – utilizate în exemplul comunicațiilor prin satelit.

Figura 4: Program de aplicație, procesor gazdă și hardware bazat pe FPGA – utilizate în exemplul comunicațiilor prin satelit.

Prin utilizarea unei interfețe de interconectare a componentelor periferice (PCI) și a accesului direct la memorie (DMA) al procesorului gazdă, performanța perifericelor crește în mod dramatic. Acest lucru se observă mai ales în cadrul îmbunătățirilor pentru procesul de derandomizare. Atunci când acest proces a fost efectuat în software-ul procesorului gazdă, a existat în mod clar un blocaj în răspunsul în timp real al sistemului. Cu toate acestea, atunci când a fost mutat pe FPGA, s-au observat următoarele beneficii:

- Procesul de derandomizare a fost executat în timp real, fără a provoca blocaje

- Sarcina de calcul a procesorului gazdă a fost redusă în mod semnificativ, iar acesta putea acum să îndeplinească mai bine rolul dorit de înregistrare.

- Performanța totală a întregului sistem a fost mărită.

Toate acestea au fost realizate fără costurile asociate cu un ASIC și beneficiind, în același timp, de flexibilitatea logicii programabile [5]. Comunicațiile prin satelit prezintă provocări considerabile, iar această abordare poate îndeplini în mod verificabil aceste cerințe și poate continua să ofere flexibilitate în proiectare.

Exemplu de infotisment pentru automobile

Sistemele de divertisment pentru automobile sunt caracteristici distinctive pentru consumatorii exigenți. Spre deosebire de majoritatea dispozitivelor electronice pentru automobile, aceste dispozitive sunt foarte vizibile și trebuie să ofere un timp de răspuns și o performanță excepționale. Cu toate acestea, proiectanții sunt deseori prinși între nevoile actuale ale proiectului și flexibilitatea pe care o vor cere caracteristicile viitoare. Pentru acest exemplu, nevoile de implementare a procesării semnalelor și a comunicațiilor wireless vor fi folosite pentru evidențierea punctelor forte ale arhitecturii hardware a coprocesorului.

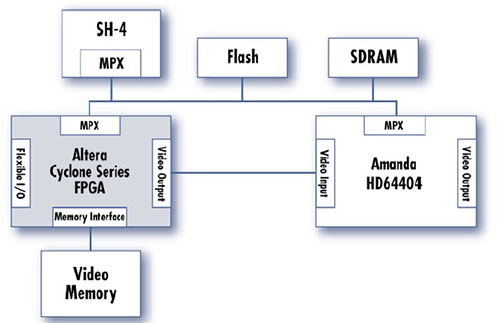

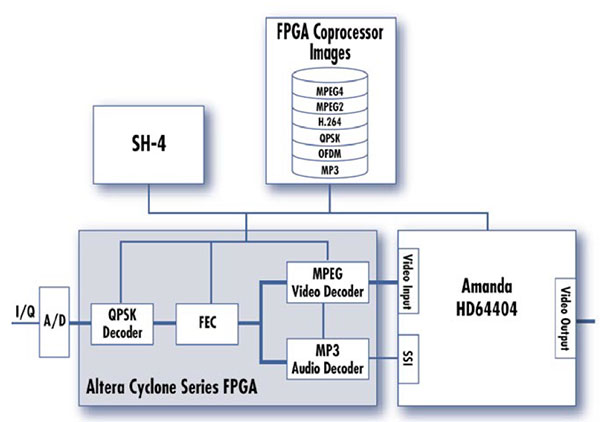

Una dintre arhitecturile predominante ale sistemelor de divertisment auto utilizate a fost publicată de corporația Delphi Delco Electronics Systems. Această arhitectură a utilizat un MCU SH-4 cu un ASIC însoțitor, perifericul Hitachi HD64404 Amanda. Această arhitectură a satisfăcut peste 75% din funcționalitatea de bază a pieței auto a divertismentului; cu toate acestea, nu avea capacitatea de a aborda aplicațiile de procesare video și comunicațiile wireless. Prin includerea unui FPGA în această arhitectură existentă, se poate adăuga o flexibilitate și o capacitate suplimentare la această abordare de proiectare deja existentă.

Figura 5: Imagine a arhitecturii coprocesorului FPGA pentru infotisment, exemplul 1.

Figura 5: Imagine a arhitecturii coprocesorului FPGA pentru infotisment, exemplul 1.

Arhitectura din Figura 5 este adecvată atât pentru procesarea video, cât și pentru managementul comunicațiilor wireless. Prin transferarea funcționalităților DSP către FPGA, procesorul Amanda poate îndeplini un rol de gestionare a sistemului și este liber să implementeze o stivă de comunicații wireless. Deoarece atât Amanda, cât și FPGA au acces la memoria externă, datele pot fi schimbate rapid între procesoarele și componentele sistemului.

Figura 6: Imagine a arhitecturii coprocesorului FPGA pentru infotisment, exemplul 2.

Figura 6: Imagine a arhitecturii coprocesorului FPGA pentru infotisment, exemplul 2.

Al doilea sistem de infotisment din Figura 6 evidențiază capacitatea FPGA de a gestiona atât datele analogice de mare viteză primite, cât și compresia și codificarea necesare pentru aplicațiile video. De fapt, toate aceste funcționalități pot fi introduse în FPGA și, prin utilizarea procesării paralele, toate acestea pot fi abordate în timp real.

Prin includerea unui FPGA într-o arhitectură hardware existentă, performanța dovedită a hardware-ului existent poate fi cuplată cu flexibilitate și siguranța pentru viitor. Chiar și în cadrul sistemelor existente, arhitectura coprocesorului oferă proiectanților opțiuni care altfel nu ar fi disponibile [6].

Avantajele prototipării rapide

În esența sa, procesul de prototipare rapidă încearcă să acopere o parte substanțială a zonei de dezvoltare a produsului prin executarea sarcinilor în paralel, prin identificarea rapidă a „erorilor” și a problemelor de proiectare și prin validarea traseelor de date și de semnal, în special a celor care se află pe traseul critic al unui proiect. Cu toate acestea, pentru ca acest proces să producă într-adevăr rezultate raționalizate și eficiente, trebuie să existe suficientă expertiză în domeniile de proiect necesare.

În mod tradițional, acest lucru înseamnă că trebuie să existe un inginer hardware, un inginer de software încorporat sau DSP și un inginer HDL. În prezent, există o mulțime de profesioniști interdisciplinari, care pot îndeplini mai multe roluri; cu toate acestea, coordonarea acestor eforturi implică încă un volum substanțial de cheltuieli de proiect.

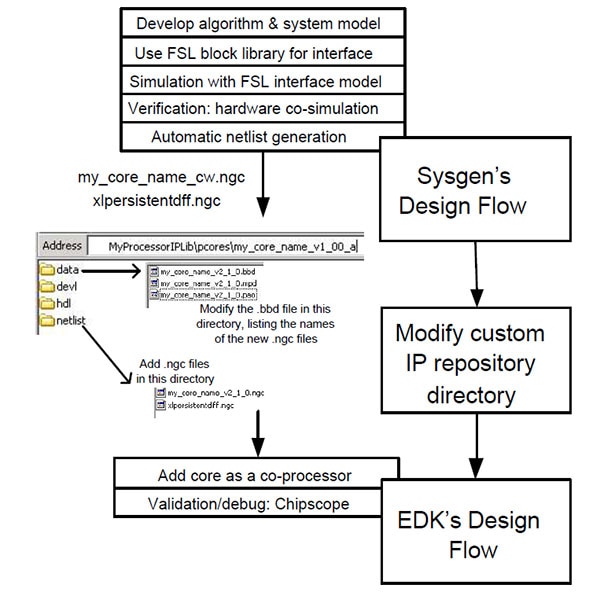

În lucrarea lor, intitulată An FPGA based rapid prototyping platform for wavelet coprocessors, autorii promovează ideea că utilizarea unei arhitecturi a coprocesorului îi permite unui singur inginer DSP să îndeplinească toate aceste roluri, în mod eficient și eficace. Pentru acest studiu, echipa a început să proiecteze și să simuleze funcționalitatea DSP dorită în cadrul instrumentului Simulink al MATLAB. Acest lucru a avut două funcții principale: 1) a verificat performanța dorită prin simulare și 2) a servit ca bază de referință față de care pot fi comparate și trimise pentru referință viitoarele opțiuni de proiectare.

După simulare, au fost identificate funcționalitățile critice și împărțite în diferite nuclee – acestea sunt componente și procesoare cu nuclee soft, care pot fi sintetizate în cadrul unui FPGA. Cel mai important pas în cadrul acestei lucrări a fost definirea interfeței dintre aceste nuclee și componente și compararea performanței schimbului de date cu performanța dorită, simulată. Acest proces de proiectare s-a aliniat îndeaproape cu fluxul de proiectare al Xilinx pentru sistemele încorporate și este rezumat în Figura 7 de mai jos.

Figura 7: Fluxul de proiectare a implementării.

Figura 7: Fluxul de proiectare a implementării.

Prin împărțirea sistemului în nuclee sintetizabile, inginerul DSP se poate concentra pe aspectele cele mai critice ale lanțului de procesare a semnalului. Nu este nevoie să fie expert în hardware sau HDL pentru a modifica, ruta sau implementa diferite procesoare sau componente de nuclee soft în cadrul FPGA. Atâta timp cât proiectantul este conștient de interfață și de formatele datelor, acesta are control deplin asupra traseelor de semnal și poate îmbunătăți performanța sistemului.

Constatări empirice – studiul de caz al transformării discrete a cosinusului

Constatările empirice nu numai că au confirmat flexibilitatea oferită de arhitectura coprocesorului proiectantului de sisteme integrate, dar au evidențiat și opțiunile de îmbunătățire a performanțelor disponibile cu instrumentele FPGA moderne. Este posibil ca îmbunătățirile, precum cele menționate mai jos, să nu fie disponibile sau să aibă un impact mai redus asupra altor arhitecturi hardware. Transformarea discretă a cosinusului (DCT) a fost selectată ca un algoritm intensiv din punct de vedere computațional, iar evoluția sa de la o implementare bazată pe C la o implementare bazată pe HDL a stat în centrul acestor constatări. A fost ales DCT, deoarece acest algoritm este utilizat în procesarea digitală a semnalelor pentru recunoașterea și filtrarea modelelor [8]. Constatările empirice s-au bazat pe un exercițiu de laborator, care a fost finalizat de către autor și colaboratori, pentru obținerea certificării Xilinx Alliance Partner pentru 2020 – 2021.

În acest efort au fost utilizate următoarele instrumente și dispozitive:

- Vivado HLS v2019

- Dispozitivul utilizat pentru evaluare și simulare a fost xczu7ev-ffvc1156-2-e

Începând cu implementarea bazată pe C, algoritmul DCT acceptă două matrice de numere pe 16 biți; matricea „a” este matricea de intrare în DCT, iar matricea „b” este matricea de ieșire din DCT. Prin urmare, lățimea datelor (DW) este definită ca 16, iar numărul de elemente din matrice (N) ca 1024/DW, adică 64. În cele din urmă, dimensiunea matricei DCT (DCT_SIZE) este setată la 8, ceea ce înseamnă că se utilizează o matrice de 8 x 8.

Urmând premisa acestui articol, implementarea algoritmului bazat pe C oferă proiectantului posibilitatea de a dezvolta și valida rapid funcționalitatea algoritmului. Deși este un aspect important, această validare acordă funcționalității o ponderare mai mare decât timpului de execuție. Această ponderare este permisă, deoarece implementarea finală a acestui algoritm va fi efectuată într-un FPGA, unde accelerarea hardware, derularea buclelor și alte tehnici sunt ușor accesibile.

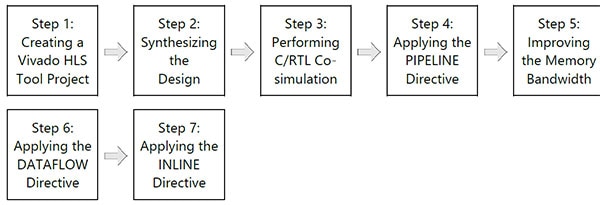

Figura 8: Fluxul de proiectare Xilinx Vivado HLS.

Figura 8: Fluxul de proiectare Xilinx Vivado HLS.

După ce codul DCT a fost creat în cadrul instrumentului Vivado HLS ca proiect, următorul pas este începerea sintetizării proiectului pentru implementarea FPGA. În cadrul acestei etape următoare devin mai evidente câteva dintre cele mai importante beneficii ale mutării execuției unui algoritm de la un MCU la un FPGA – ca referință, această etapă este echivalentă cu etapa-cheie de gestionare a sistemului cu ajutorul microcontrolerului, discutată mai sus.

Instrumentele FPGA moderne permit o suită de optimizări și îmbunătățiri care sporesc considerabil performanța algoritmilor complecși. Înainte de a analiza rezultatele, trebuie să țineți cont de câțiva termeni importanți:

- Latență – numărul de cicluri de ceas necesare pentru a executa toate iterațiile buclei [10]

- Interval – numărul de cicluri de ceas înainte ca următoarea iterație a unei bucle să înceapă să proceseze datele [11]

- BRAM – memorie cu acces aleatoriu în bloc

- DSP48E – secțiune de procesare digitală a semnalelor pentru arhitectura UltraScale

- FF – sistem flipflop

- LUT – tabel de căutare

- URAM – memorie unificată cu acces aleatoriu (poate fi compusă dintr-un singur tranzistor)

|

||||||||||||||||||||||||||||||||||||||||

Tabelul 1: Rezultatele optimizării execuției algoritmului FPGA (latență și interval).

|

Tabelul 2: Rezultatele optimizării execuției algoritmului FPGA (utilizarea resurselor).

Implicit

Setarea implicită pentru optimizare provine din rezultatul nealterat al traducerii algoritmului bazat pe C în HDL sintetizabil. Nu este activată nicio optimizare, iar aceasta poate fi utilizată ca referință de performanță pentru a înțelege mai bine celelalte optimizări.

Bucla internă a secvenței pipeline

Directiva PIPELINE instruiește Vivado HLS să deruleze buclele interne, astfel încât să poată începe procesarea noilor date în timp ce datele existente se află încă în secvența pipeline. Astfel, noile date nu trebuie să aștepte ca datele existente să fie complete înainte de a începe procesarea.

Bucla externă a secvenței pipeline

Prin aplicarea directivei PIPELINE la bucla externă, operațiile buclei externe sunt incluse acum în secvența pipeline. Cu toate acestea, operațiile buclelor interne au loc acum în mod concurent. Atât timpul de latență, cât și timpul de interval sunt reduse la jumătate prin aplicarea directă la bucla externă.

Partiție de matrice

Această directivă cartografiază conținutul buclelor în matrice și, astfel, simplifică toate accesările de memorie la elemente individuale din aceste tipuri de matrice. În acest fel, se consumă mai multă memorie RAM, dar, din nou, timpul de execuție al acestui algoritm este redus la jumătate.

Fluxul de date

Această directivă oferă proiectantului posibilitatea de a specifica numărul țintă de cicluri de ceas între fiecare dintre citirile datelor de intrare. Această directivă este acceptată numai pentru funcția de nivel superior. Numai buclele și funcțiile expuse la acest nivel vor beneficia de această directivă.

În linie

Directiva ÎN LINIE aplatizează toate buclele, atât cele interne, cât și cele externe. Atât procesele de rânduri, cât și cele de coloane pot fi executate acum simultan. Numărul de cicluri de ceas necesare este redus la minimum, chiar dacă acest lucru consumă mai multe resurse FPGA.

Concluzie

Arhitectura hardware a coprocesorului oferă proiectantului de sisteme integrate o platformă de înaltă performanță care își păstrează flexibilitatea de proiectare pe parcursul dezvoltării și după lansarea produsului. Validând mai întâi algoritmii în C sau C++, procesele, traseele de date și de semnal și funcționalitatea critică pot fi verificate într-un timp relativ scurt. Apoi, prin transpunerea algoritmilor cu procesor intensiv în FPGA-ul coprocesorului, proiectantul se poate bucura de avantajele accelerării hardware și de un design mai modular.

În cazul în care anumite piese devin inactuale sau sunt necesare optimizări, aceeași arhitectură poate permite aceste modificări. Noi MCU-uri și noi FPGA-uri pot fi integrate în proiect, în timp ce interfețele pot rămâne relativ neatinse. În plus, deoarece atât MCU-urile, cât și FPGA-urile pot fi actualizate pe teren, modificările și optimizările specifice utilizatorului pot fi aplicate pe teren și de la distanță.

În concluzie, această arhitectură combină viteza de dezvoltare și disponibilitatea unui MCU cu performanța și capacitatea de extindere a unui FPGA. Cu optimizări și îmbunătățiri ale performanței disponibile în fiecare etapă de dezvoltare, arhitectura coprocesorului poate satisface chiar și cele mai dificile cerințe – atât pentru proiectele actuale, cât și pentru cele viitoare.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.