Îndepliniți diverse cerințe funcționale și de siguranță cu procesoarele cu nuclee multiple

Contributed By DigiKey's North American Editors

2020-10-01

Se așteaptă ca aplicațiile pentru automobile, industrii, robotică, controlul clădirilor și alte aplicații critice din sistemele încorporate să înceapă să preia sarcini de lucru mai diverse, care se extind de la monitorizarea în timp real cu putere redusă la aplicații multimedia de nivel înalt, cu afișaje grafice cu ecrane multiple, destinate interfețelor om-mașină (HMI). În timp ce îndeplinesc aceste cerințe funcționale ample, acestea trebuie să poată oferi și standarde stricte de siguranță, costuri și impacturi reduse și să optimizeze echilibrul putere/performanță.

Până acum, pentru a îndeplini aceste cerințe care, de multe ori, sunt contradictorii, dezvoltatorii au fost obligați fie să sacrifice capacitatea funcțională, fie să complice designul și producția cu dispozitive suplimentare necesare pentru îndeplinirea cerințelor specifice pentru grafică, securitate și siguranță, printre altele. De fapt, dezvoltatorii au nevoie de o singură soluție care poate susține o gamă amplă de produse ce îndeplinesc aceste cerințe într-o varietate mare de aplicații ale sistemelor încorporate critice.

Acest articol descrie rapid evoluția designului sistemelor critice încorporate. Apoi va arăta modul în care procesoarele de aplicații cu nuclee multiple – proiectate special de NXP Semiconductors pentru a susține o listă din ce în ce mai amplă de cerințe, atât pentru funcționalitate extinsă, cât și pentru funcții de siguranță certificate – pot fi utilizate pentru a răspunde provocărilor cu care se confruntă dezvoltatorii.

Evoluția considerentelor legate de proiectarea sistemelor încorporate

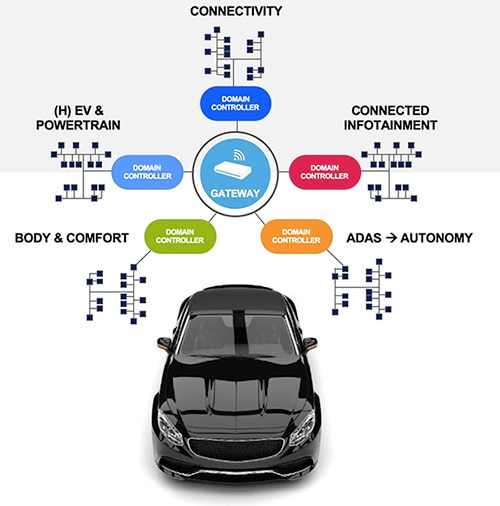

Rolul tradițional al dispozitivelor încorporate în susținerea unui set limitat de funcții ale sistemului a fost în mare parte înlocuit de cererea de dispozitive care oferă funcții extinse. De exemplu, în aplicațiile industriale, nevoia de funcții HMI îmbunătățite în instrumentele și echipamentele inteligente vine cu nevoia de procesoare capabile să ofere grafică optimizată, îndeplinind simultan cerințele industriale mai tradiționale în timp real. În mod similar, tendința aplicațiilor auto de a se îndrepta spre arhitecturi ierarhice alcătuite din clustere de domenii funcționale și gateway-uri determină apariția nevoii de procesoare complet capabile să îndeplinească aceste cerințe (Figura 1).

Figura 1: tendința către arhitecturi de sisteme auto mai ierarhizate a creat o nevoie de soluții de procesoare mai integrate și scalabile. (Sursă imagine: NXP Semiconductors)

Figura 1: tendința către arhitecturi de sisteme auto mai ierarhizate a creat o nevoie de soluții de procesoare mai integrate și scalabile. (Sursă imagine: NXP Semiconductors)

În fiecare domeniu funcțional, cererea de funcții mai sofisticate continuă să ridice pragul pentru performanță și funcții integrate. De exemplu, apariția afișajelor la nivelul capului necesită soluții capabile să asigure livrarea continuă de informații grafice vitale pentru șoferi. Împreună cu aceste afișaje de ultimă generație, nevoia din ce în ce mai mare de conștientizare sporită a șoferului vine cu cerințe suplimentare pentru interfețele camerelor și execuția de înaltă performanță a unui software avansat de recunoaștere care poate asigura detectarea stării de somnolență.

Pe măsură ce aplicațiile continuă să evolueze, nevoia de soluții extrem de integrate și scalabile devine mai urgentă, pentru a îndeplini cerințe din ce în ce mai diverse, reducând în același timp impactul, costurile și complexitatea designului. Prin utilizarea familiei de procesoare pentru aplicații i.MX 8 de la NXP, dezvoltatorii pot beneficia de o platformă compatibilă de procesoare cu gama de funcții și performanțe necesară pentru susținerea unei ample varietăți de cerințe ale aplicațiilor. În cadrul familiei i.MX 8, seria i.MX 8X NXP răspunde noilor cerințe de procesoare cu siguranță certificată, necesare în aplicațiile industriale și auto de nivel mediu.

Arhitectura cu nuclee multiple gestionează diverse sarcini de lucru

Una dintre dificultățile cu care se confruntă dezvoltatorii în implementarea dispozitivelor pentru aplicații auto și industriale este varietatea amplă de cerințe. Acolo unde dezvoltatorii s-ar putea aștepta să abordeze sarcini de lucru pentru procesarea aplicațiilor fie în timp real, fie la nivel înalt, cererea de subsisteme inteligente a combinat aceste tipuri de calcul extrem de diferite. Din ce în ce mai mult, dezvoltatorii au nevoie de soluții care pot oferi atât un răspuns de încredere în timp real, cât și execuție de înaltă performanță pentru aplicații, respectând în același timp cerințele de siguranță funcțională.

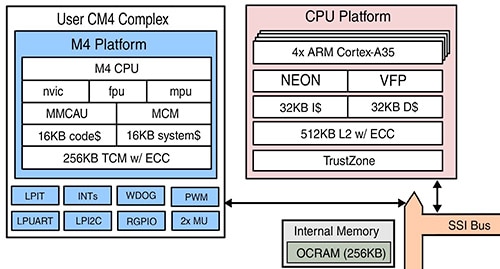

Proiectate pentru a oferi funcții în timp real, procesare de înaltă performanță și consum redus de energie, procesoarele din seria i.MX 8X NXP profită din plin de arhitectura unei unități de procesare centrală (CPU) sofisticată, cu nuclee multiple, pentru a gestiona diverse sarcini de lucru de calcul (Figura 2).

Figura 2: seria i.MX 8X NXP folosește o arhitectură cu nuclee multiple care include un procesor încorporat Arm Cortex-M4 (CM4) și mai multe procesoare de aplicații Arm Cortex-A35 pentru a accepta sarcini de lucru pentru diverse software-uri. (Sursă imagine: NXP Semiconductors)

Figura 2: seria i.MX 8X NXP folosește o arhitectură cu nuclee multiple care include un procesor încorporat Arm Cortex-M4 (CM4) și mai multe procesoare de aplicații Arm Cortex-A35 pentru a accepta sarcini de lucru pentru diverse software-uri. (Sursă imagine: NXP Semiconductors)

Pentru sarcinile generale de procesare în timp real, dispozitivele i.MX 8X includ un procesor Arm Cortex-M4 (CM4) cu unitate cu punct flotant (FPU), unitate de protecție a memoriei (MPU), unitate de accelerare criptografică mapată în memorie (MMCAU) și modul de control divers (MCM). Pentru a susține perifericele externe, precum senzorii și mecanismele de acționare, acest complex CM4 pentru utilizator combină un controler de întrerupere vectorial imbricat (NVIC) cu un set complex de interfețe și module, inclusiv cu un temporizator de întrerupere periodică de putere redusă (LPIT), modulația impulsului în lățime (PWM) și alte funcții care sunt în mod obișnuit necesare în aplicațiile auto și cele industriale. O pereche de memorii cache și memorie strâns cuplată (TCM) cu funcție de cod de corectare a erorilor (ECC) ajută la minimizarea accesului la memoria externă, accelerarea execuției și gestionarea erorilor de memorie.

Pentru executarea rapidă a sarcinilor de lucru ale aplicației, platforma CPU include mai multe procesoare de aplicații Arm Cortex-A35 (AP-uri) cu consum de energie redus – două AP-uri în procesoare 8DualXPlus precum MIMX8UX6AVLFZAC și patru AP-uri în procesoare 8QuadXPlus precum MIMX8QX6AVLFZAC. Împreună cu instrucțiunile dedicate (I$) și memoria cache de date (D$), platforma CPU include o memorie cache partajată de nivelul 2 (L2) de 512 kilobytes (Kbyte) cu ECC.

Nucleele Arm Cortex-A35 ale arhitecturii oferă atât compatibilitate pentru software, cât și scalabilitatea performanței, acceptând atât compatibilitatea cu versiunile ulterioare de 32 biți, cât și performanța pentru 64 biți. Pentru a accelera și mai mult execuția algoritmilor intensivi de calcul, cum ar fi procesarea semnalului și învățarea automatizată, procesoarele Arm Cortex-A35 oferă procesare cu punct flotant vectorial (VFP) și extensii de arhitectură cu date multiple și o singură instrucțiune (SIMD) Neon de la Arm. Pentru a accelera execuția software-ului pentru procesarea imaginilor, vederea computerizată și învățarea automatizată, Arm Compute Library oferă funcții optimizate pentru arhitecturile procesorului Arm și ale unității de procesare grafică (GPU), iar biblioteca open source Ne10 C oferă funcții optimizate Arm pentru operațiuni intensive de calcul.

Motoarele dedicate elimină sarcina CPU-urilor principale

Pe lângă complexul CM4 al utilizatorului și platforma CPU Arm Cortex-A35 cu nuclee multiple, arhitectura oferă motoare dedicate suplimentare pentru aplicații multimedia. Împreună cu un procesor de semnal digital (DSP) pentru procesarea codecurilor audio și vocale, arhitectura integrează atât o unitate GPU, cât și o unitate de procesare video (VPU). GPU-ul dispozitivului acceptă biblioteci grafice standard, accelerând operațiunile prin intermediul a patru vectori separați cu punct flotant, din patru componente (vec4), cu 16 unități de execuție și un motor bit blit bidimensional de performanță ridicată. VPU gestionează formate video populare, accelerând decodarea până la 4Kp30 (progresiv, 30 Hz) și codând până la 1080p30. La rândul său, blocul controlerului de afișaj dedicat al cipului poate acționa ieșirea plăcii grafice până la trei afișaje independente.

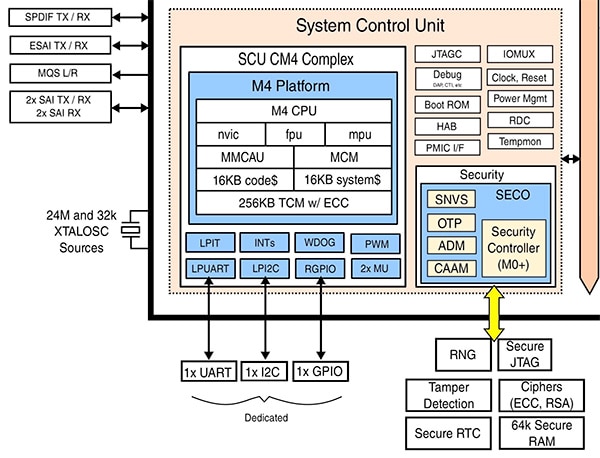

În plus, pentru a maximiza în continuare performanța, arhitectura i.MX 8X integrează și nuclee de procesor suplimentare, concepute pentru a elibera platformele CPU principale de sarcina de procesare suplimentară suportată, de obicei, la executarea serviciilor de gestionare și de securitate ale sistemului. Pentru gestionarea sistemului, unitatea de control al sistemului (SCU) a arhitecturii integrează un complex CM4 care se potrivește cu complexul CM4 al utilizatorului, dar rămâne dedicat complet operațiunilor SCU și nu poate fi accesat și utilizat de către dezvoltatori (Figura 3).

Figura 3: integrat adânc în procesoarele i.MX 8X NXP și nefiind disponibil dezvoltatorilor, SCU utilizează un subsistem dedicat Arm Cortex-M4 (CM4) pentru a transfera sarcinile de gestionare a sistemului de la procesoarele principale ale dispozitivului. (Sursă imagine: NXP Semiconductors)

Figura 3: integrat adânc în procesoarele i.MX 8X NXP și nefiind disponibil dezvoltatorilor, SCU utilizează un subsistem dedicat Arm Cortex-M4 (CM4) pentru a transfera sarcinile de gestionare a sistemului de la procesoarele principale ale dispozitivului. (Sursă imagine: NXP Semiconductors)

Pe lângă gestionarea alimentării, a sincronizării și a altor funcții interne, SCU controlează multiplexarea pinilor și puterea unității de acționare a canalului de intrare/ieșire (I/O) la funcționare normală. De fapt, complexul CM4 al utilizatorului și AP-urile Arm Cortex-A35 nu pot accesa direct aceste funcții hardware variate de nivel scăzut. În schimb, SCU se utilizează pentru abstractizarea acestor funcții, astfel ca software-ul care rulează pe CM4 al utilizatorului sau pe AP-uri trebuie pur și simplu să apeleze funcțiile interfeței de programare a aplicației (API) pentru firmware SCU, pentru a îndeplini funcții precum oprirea domeniilor de alimentare inutile. De exemplu, dacă acel domeniu de alimentare este partajat cu un alt procesor, SCU recunoaște pur și simplu cererea de oprire, dar menține domeniul alimentat până când și celălalt procesor emite o cerere de oprire.

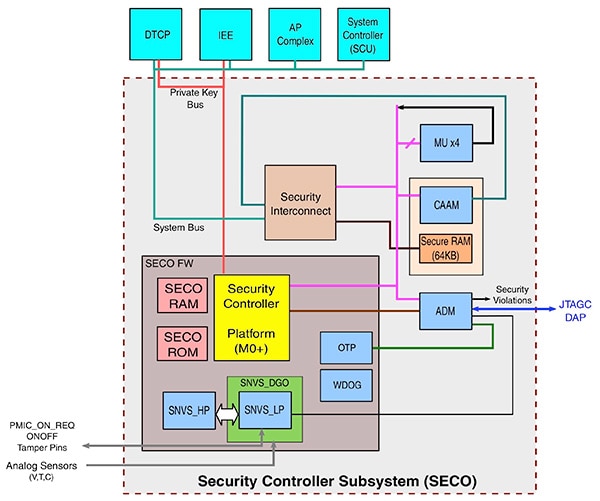

Pentru a gestiona compatibilitatea de securitate extinsă a dispozitivului i.MX 8X, în subsistemul controlerului de securitate a dispozitivului (SECO) se activează un alt procesor dedicat. În subsistemul SECO, un procesor integrat Arm Cortex-M0+ de putere redusă execută firmware-ul care acceptă funcții de securitate bazate pe hardware, inclusiv accesul printr-o magistrală privată pentru cheile de securitate, memorie programabilă de unică folosință (OTP) pentru stocarea cheilor de securitate și stocare non-volatilă securizată (SNVS) pentru date private suplimentare sau chei temporare (Figura 4).

Figura 4: în subsistemul controlerului de securitate i.MX 8X NXP (SECO), un procesor dedicat Arm Cortex-M0+ de putere scăzută gestionează operațiunile de securitate, bazându-se pe o magistrală de chei private și mai multe module hardware pentru stocare sigură, accelerarea criptografiei și acces autentificat pentru depanare. (Sursă imagine: NXP Semiconductors)

Figura 4: în subsistemul controlerului de securitate i.MX 8X NXP (SECO), un procesor dedicat Arm Cortex-M0+ de putere scăzută gestionează operațiunile de securitate, bazându-se pe o magistrală de chei private și mai multe module hardware pentru stocare sigură, accelerarea criptografiei și acces autentificat pentru depanare. (Sursă imagine: NXP Semiconductors)

Dincolo de aceste mecanisme de securitate de bază, subsistemul SECO coordonează operațiunile de securitate pentru detectarea manipulării nepermise și depanarea securizată accesate prin modulul său autentificat de depanare (ADM). Pentru o execuție securizată, modulul de accelerare și asigurare criptografică (CAAM) integrat acceptă o suită completă de algoritmi de securitate, inclusiv criptografie simetrică și asimetrică, funcții de criptare hash și un generator de numere aleatorii (RNG).

În funcționare normală, unitățile de procesare ale dispozitivelor, inclusiv SCU, AP-urile și acceleratorul de protecție a conținutului pentru transportul digital (DTCP) utilizează interconectarea de securitate SECO pentru a accesa funcționalitatea CAAM prin magistrala de sistem. În afară de accesul prin funcționalitatea de acces direct la memorie CAAM (DMA), procesorul dedicat Cortex-M0+ al SECO nu poate accesa magistrala de sistem. În schimb, acesta utilizează conexiuni interne protejate pentru a accesa perifericele, memoria securizată cu acces aleator (RAM) și memoria doar pentru citire (ROM), precum și magistrala sa specială pentru chei private.

Împreună cu utilizarea acceleratorului DTCP, această magistrală pentru chei private are un rol central în capacitatea procesorului i.MX 8X de a oferi criptare și decriptare din mers. Aici, procesorul de securitate își folosește resursele pentru a furniza cheile private necesare pentru modulul motorului de criptare/decriptare în linie (IEE), pe măsură ce citește sau inscripționează în mod securizat în spațiul de stocare criptat, fără implicarea procesorului care face cererea, a controlerului DMA sau a dispozitivului I/O.

Bazându-se pe tehnologia TrustZone de la Arm, integrată în procesoarele Cortex-A35 ale dispozitivului, subsistemul SECO funcționează și cu SCU în timpul procesului de inițializare securizată. În acest proces, SCU interpretează setările de inițializare, configurează sursele de inițializare și încarcă imaginile de inițializare în memoria internă sau externă. La rândul său, subsistemul SECO își folosește funcțiile de criptografie pentru a autentifica imaginile firmware semnate după ce sunt încărcate, dar înainte de a fi executate.

Protejarea funcționalității esențiale pentru control și afișare

Deși capacitatea de procesare eficientă și sigură a diverselor sarcini de lucru este importantă, pentru aplicațiile esențiale, cum ar fi cele din segmentele auto și industriale, capacitatea de a proteja funcțiile cheie este la fel de vitală. Familia i.MX 8X de la NXP combină funcțiile sale de procesare cu funcțiile de siguranță certificabilă necesare pentru îndeplinirea acestor cerințe critice.

Suportul de siguranță al familiei de procesoare este încorporat la mai multe niveluri, începând cu fabricarea într-o tehnologie de procesare cu siliciu complet epuizat pe izolator (FD-SOI) care îmbunătățește fiabilitatea sistemului. Deoarece siguranța sistemului depinde de o bază solidă de securitate, combinația dintre AP-urile compatibile TrustZone, subsistemul SECO și funcțiile de inițializare securizate poate asigura tipul de mediu de încredere necesar pentru contracararea amenințărilor la adresa siguranței și securității.

În același timp, capacitatea de a gestiona în mod independent sarcinile pentru care timpul este esențial, folosind complexul CM4 al utilizatorului, și capacitatea de a descărca sarcini de sistem critice în subsistemele SCU și SECO ajută la asigurarea faptului că funcțiile esențiale ale aplicației rămân disponibile în ciuda sarcinii de procesare variate. De fapt, NXP extinde acest concept pentru a susține afișajele esențiale prin tehnologia SafeAssure a companiei, care integrează o cale de revenire după eroare a afișajului hardware compatibil cu nivelul B de integritate a siguranței auto (ASIL B) în dispozitivele i.MX 8X. Cu SafeAssure, utilizatorii primesc automat o imagine de revenire din starea de eroare dacă dispozitivul detectează o eroare de integritate a datelor sau de GPU. Funcționând în fundal, această imagine de revenire din starea de eroare garantează că informațiile critice rămân disponibile chiar și în timpul defectării afișajului principal.

Suportul pentru aplicațiile de siguranță se extinde la accesul la memorie în sistemele bazate pe i.MX 8X. Printre interfețele de memorie acceptate de acestea, dispozitivele i.MX 8X oferă ECC pe 8 biți pentru memorie Double Data Rate 3 (DDR3L) de joasă tensiune. Împreună cu ECC în memoria cache L2 (consultați din nou Figura 2), această funcție ECC DDR3L acceptă nivelul 3 de integritate a siguranței industriale (SIL 3). De asemenea, arhitectura i.MX 8X extinde compatibilitatea ECC pentru dispozitivele de stocare flash externe. Aici, un codificator integrat Bose, Ray-Chaudhuri, Hocquenghem (BCH) și un modul de decodare oferă ECC pe 62 biți, care poate corecta de la 2 până la 20 de erori de un singur bit într-un bloc de date citite de pe aceste dispozitive de stocare.

Deschiderea aplicațiilor bazate pe i.MX 8X

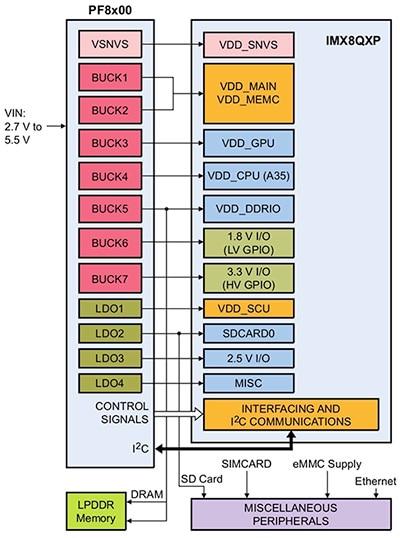

Ca și în cazul oricărui procesor din această clasă, implementarea unui design bazat pe i.MX 8X necesită atenție sporită cu privire la cerințele stricte de alimentare, inclusiv secvențele critice de pornire. Pornirea dispozitivelor i.MX 8X necesită pornirea în secvență sau simultan în patru grupuri diferite de alimentare, începând cu subsistemul SVNS și continuând cu SCU, intrările/ieșirile și interfețele de memorie și, în final, cu restul dispozitivului. Dezvoltatorii pot îndeplini această cerință pur și simplu utilizând dispozitivele cu circuit integrat de gestionare a energiei (PMIC) PF8x00 de la NXP, care oferă un set complet de șine de tensiune și semnale de control necesare pentru susținerea procesoarelor i.MX 8X, precum și a memoriei externe și a perifericelor tipice ale sistemului (Figura 5) .

Figura 5: PMIC-urile PF8x00 NXP oferă un set complet de șine de tensiune și semnale de control necesare pentru alimentarea procesoarelor i.MX 8X. (Sursă imagine: NXP Semiconductors)

Figura 5: PMIC-urile PF8x00 NXP oferă un set complet de șine de tensiune și semnale de control necesare pentru alimentarea procesoarelor i.MX 8X. (Sursă imagine: NXP Semiconductors)

În implementarea propriilor designuri bazate pe i.MX 8X, dezvoltatorii pot utiliza PMIC MC33PF8100CCES NXP, care este preprogramat pentru utilizare cu procesoare 8QuadXPlus, cum ar fi MIMX8QX6AVLFZAC. Alte variante PF8x00, precum MC33PF8100A0ES și MC33PF8200A0ES acceptă procesoare i.MX 8X, dar nu sunt preprogramate.

Pentru aplicații de siguranță, dispozitivele din seria PF8200, cum ar fi MC33PF8200A0ES, integrează caracteristici concepute pentru a susține sistemele ASIL B. Împreună cu mai multe monitoare interne, inclusiv cu un monitor de tensiune de ieșire cu o referință dedicată pentru bandă, PMIC-urile PF8200 includ un pin de ieșire autoprotejat (FSOB) conceput pentru a menține sistemul într-o stare sigură în timpul pornirii sau în timpul unui eveniment de cădere de tensiune. În plus, o rutină de auto-testare analogică integrată (ABIST) testează toate monitoarele de tensiune, în timp ce o rutină de auto-testare verifică funcționalitatea altor dispozitive.

Deși PMIC-urile PF8x00 pot simplifica designul hardware al sistemelor bazate pe i.MX 8X, este posibil ca unii dezvoltatori să fie nevoiți să înceapă imediat să evalueze dispozitivele i.MX 8X și să creeze rapid prototipuri pentru aplicațiile bazate pe i.MX 8X. Kitul de activare a multisenzorilor (MEK) MCIMX8QXP-CPU i.MX 8X de la NXP oferă o platformă de dezvoltare pregătită, care combină un procesor i.MX 8QuadXPlus NXP, PMIC F8100 NXP, RAM de 3 gigabytes (Gbyte), memorie de controler multimedia încorporat (eMMC) de 32 Gbytes și memorie flash de 64 megabytes (Mbyte). Împreună cu afișajul, camera și interfețele audio, placa MEK include un set de senzori utilizați în mod obișnuit în aplicații auto sau industriale. De asemenea, pentru opțiuni suplimentare de conectivitate, audio și expansiune, dezvoltatorii pot adăuga și placa de bază MCIMX8-8X-BB opțională de la NXP.

Concluzie

Pentru un număr din ce în ce mai mare de aplicații, precum cele pentru domeniul auto, domeniul industrial, controlul clădirilor și HMI-uri, sarcinile de lucru de procesare s-au extins pentru a include atât procesarea tradițională în timp real a intrării/ieșirii, cât și o nouă procesare la nivel de aplicație cu grafică multimedia. Deși există opțiuni de design pentru fiecare tip de sarcină de lucru, puține soluții disponibile răspund nevoii tot mai mari de soluții de performanță ridicată și cu consum redus de energie capabile să îndeplinească cerințele pentru designurile cu siguranță certificată în aplicațiile auto și industriale.

După cum se arată, prin utilizarea unei familii de procesoare cu nuclee multiple de la NXP Semiconductors, dezvoltatorii pot implementa mai eficient designuri capabile să îndeplinească aceste cerințe diverse și să le scaleze cu ușurință, pentru a răspunde noilor cerințe de performanță ridicată.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.